# Serial ATA International Organization:

# Serial ATA Revision 3.0

## RELEASE CANDIDATE 1 1-March-2009

**SATA-IO Board Members:**

Dell Computer Corporation Hewlett Packard Corporation Hitachi Global Storage Technologies, Inc. Intel Corporation Maxim Integrated Products Seagate Technology Western Digital Corporation Serial ATA International Organization: Serial ATA Revision 3.0 specification ("Final Specification") is available for download at www.sata-io.org.

#### SPECIFICATION DISCLAIMER

THIS SPECIFICATION IS PROVIDED TO YOU "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE. THE AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OR IMPLEMNETATION OF INFORMATION IN THIS SPECIFICATION. THE AUTHORS DO NOT WARRANT OR REPRESENT THAT SUCH USE WILL NOT INFRINGE SUCH RIGHTS. THE PROVISION OF THIS SPECIFICATION TO YOU DOES NOT PROVIDE YOU WITH ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS.

Copyright 2002-2009, Serial ATA International Organization. All rights reserved.

For more information about Serial ATA, refer to the Serial ATA International Organization website at <u>www.sata-io.org</u>.

All product names are trademarks, registered trademarks, or servicemarks of their respective owners.

Serial ATA International Organization contact information:

SATA-IO 3855 SW 153<sup>rd</sup> Drive Beaverton, Oregon 97006 USA Tel: +1 503-619-0572 Fax: +1 503-644-6708 E-mail: <u>admin@sata-io.org</u>

## TABLE OF CONTENTS

| 1 |        | on History                                       |      |

|---|--------|--------------------------------------------------|------|

|   |        | vision 2.5 (Ratification Date October 27, 2005)  |      |

|   | 1.2 Re | vision 2.6 (Ratification Date February 15, 2007) | . 23 |

|   |        | vision 3.0 (Release Candidate 1, March 1, 2009)  |      |

| 2 |        |                                                  |      |

| 3 |        | tive references                                  |      |

|   |        | proved references                                |      |

|   |        | ferences under development                       |      |

|   |        | ner references                                   |      |

| 4 |        | ons, abbreviations, and conventions              |      |

|   |        | finitions and abbreviations                      |      |

|   | 4.1.1  | Active Port                                      |      |

|   | 4.1.2  | ATA (AT Attachment)                              |      |

|   | 4.1.3  | ATAPI (AT Attachment Packet Interface) device    |      |

|   | 4.1.4  | BER (bit error rate)                             |      |

|   | 4.1.5  | bitrate                                          |      |

|   | 4.1.6  | bit synchronization                              |      |

|   | 4.1.7  | burst                                            |      |

|   | 4.1.8  | byte                                             |      |

|   | 4.1.9  | character                                        |      |

|   | 4.1.10 | character alignment                              |      |

|   | 4.1.11 | character slipping                               |      |

|   | 4.1.12 | ClickConnect                                     |      |

|   | 4.1.13 | CLTF (Closed Loop Transfer Function)             |      |

|   | 4.1.14 | code violation                                   |      |

|   | 4.1.15 | comma character                                  |      |

|   | 4.1.16 | comma sequence                                   |      |

|   | 4.1.17 | command aborted                                  |      |

|   | 4.1.18 | command completion                               |      |

|   | 4.1.19 | command packet                                   |      |

|   | 4.1.20 | concentrator                                     |      |

|   | 4.1.21 | Control Block registers                          |      |

|   | 4.1.22 | control character                                |      |

|   | 4.1.23 | control port                                     |      |

|   | 4.1.24 | control variable                                 |      |

|   | 4.1.25 | CRC (Cyclic Redundancy Check)                    |      |

|   | 4.1.26 | data character                                   |      |

|   | 4.1.27 | data signal source                               |      |

|   | 4.1.28 | device                                           |      |

|   | 4.1.29 | device port                                      |      |

|   | 4.1.30 | DCB (DC block)                                   |      |

|   | 4.1.31 | differential signal                              |      |

|   | 4.1.32 | DJ (deterministic jitter – peak to peak)         |      |

|   | 4.1.33 | DMA (direct memory access)                       |      |

|   | 4.1.34 | Dword                                            |      |

|   | 4.1.35 | Dword synchronization                            |      |

|   | 4.1.36 | EMI (Electromagnetic Interference)               |      |

|   | 4.1.37 | encoded character                                |      |

|   | 4.1.38 | endpoint device                                  |      |

|   | 4.1.39 | elasticity buffer                                |      |

|   | 4.1.40 | eSATA                                            |      |

|   | 4.1.41 | Fbaud                                            |      |

|   | 4.1.42 | FER (frame error rate)                           | . 35 |

| 4 4 4 9          | First party DMA Data Dhasa                            | 25 |

|------------------|-------------------------------------------------------|----|

| 4.1.43<br>4.1.44 | First-party DMA Data Phase<br>First-party DMA access  |    |

| 4.1.44           | FIS (Frame Information Structure)                     | 30 |

| 4.1.45           |                                                       |    |

|                  | frame<br>Gen1                                         |    |

| 4.1.47           |                                                       |    |

| 4.1.48           | Gen1i                                                 |    |

| 4.1.49           | Gen1m                                                 |    |

| 4.1.50           | Gen1x                                                 |    |

| 4.1.51           | Gen2                                                  |    |

| 4.1.52           | Gen2i                                                 |    |

| 4.1.53           | Gen2m                                                 |    |

| 4.1.54           | Gen2x                                                 | 36 |

| 4.1.55           | Gen3                                                  |    |

| 4.1.56           | Gen3i                                                 | 36 |

| 4.1.57           | HBA (Host Bus Adapter)                                | 36 |

| 4.1.58           | HBWS (High Bandwidth Scope)                           | 36 |

| 4.1.59           | HFTP (High Frequency Test Pattern)                    |    |

| 4.1.60           | hot plug                                              |    |

| 4.1.61           | host port                                             |    |

| 4.1.62           | inactive port                                         |    |

| 4.1.63           | interrupt pending                                     |    |

| 4.1.64           | immediate NCQ command                                 |    |

| 4.1.65           | ISI (inter-symbol interference)                       |    |

| 4.1.66           | JMD (jitter measuring device)                         |    |

|                  |                                                       |    |

| 4.1.67           | JTF (Jitter Transfer Function)                        |    |

| 4.1.68           | junk                                                  |    |

| 4.1.69           | LBA (Logical Block Address)                           |    |

| 4.1.70           | LBP (Lone Bit Pattern)                                |    |

| 4.1.71           | LED (Light Emitting Diode)                            |    |

| 4.1.72           | legacy mode                                           |    |

| 4.1.73           | legal character                                       |    |

| 4.1.74           | LFSR (Linear Feedback Shift Register)                 |    |

| 4.1.75           | LFTP (low frequency test pattern)                     |    |

| 4.1.76           | LL (laboratory load)                                  |    |

| 4.1.77           | LSS (laboratory sourced signal or lab-sourced signal) | 38 |

| 4.1.78           | MFTP (mid frequency test pattern)                     | 38 |

| 4.1.79           | NCQ streaming command                                 | 38 |

| 4.1.80           | NCQ Non-streaming command                             | 38 |

| 4.1.81           | OOB (Out-of-Band signaling)                           | 38 |

| 4.1.82           | OS-aware hot plug                                     |    |

| 4.1.83           | OS-aware hot removal                                  |    |

| 4.1.84           | Phy offline                                           |    |

| 4.1.85           | PIO (programmed input/output)                         |    |

| 4.1.86           | port address                                          |    |

| 4.1.87           | PRD (Physical Region Descriptor)                      |    |

| 4.1.88           | primitive                                             |    |

| 4.1.89           | protocol-based port selection                         |    |

| 4.1.90           | quiescent power condition                             |    |

|                  |                                                       |    |

| 4.1.91           | RJ (random jitter)                                    |    |

| 4.1.92           | SECTOR                                                |    |

| 4.1.93           | SEMB (Serial ATA Enclosure Management Bridge)         |    |

| 4.1.94           | SEP (Storage Enclosure Processor)                     |    |

| 4.1.95           | Shadow Register Block registers                       |    |

| 4.1.96           | side-band port selection                              |    |

| 4.1.97           | SMART                                                 |    |

| 4.1.98           | SSC (spread spectrum clocking)                        | 40 |

|                  |                                                       |    |

|   | 4.1.99  | surprise hot plug                                                      |      |

|---|---------|------------------------------------------------------------------------|------|

|   | 4.1.100 | surprise hot removal                                                   | . 40 |

|   | 4.1.101 | SYNC Escape                                                            | . 40 |

|   | 4.1.102 | TDR (time domain reflectometer)                                        | . 40 |

|   | 4.1.103 | TIA (timing interval analyzer)                                         | . 41 |

|   | 4.1.104 | TJ (total jitter)                                                      |      |

|   | 4.1.105 | UI (unit interval)                                                     |      |

|   | 4.1.106 | unrecoverable error                                                    |      |

|   | 4.1.107 | UUT (unit under test)                                                  |      |

|   | 4.1.108 | VNA (vector network analyzer)                                          |      |

|   | 4.1.109 | warm plug                                                              |      |

|   | 4.1.110 | word                                                                   |      |

|   | 4.1.111 | xSATA                                                                  |      |

|   | 4.1.112 | zero crossing                                                          |      |

|   |         | ventions                                                               |      |

|   | 4.2.1   | Precedence                                                             |      |

|   | 4.2.2   | Keywords                                                               |      |

|   | 4.2.3   | Numbering                                                              |      |

|   | 4.2.4   | Dimensions                                                             |      |

|   | 4.2.5   | Signal conventions                                                     |      |

|   | 4.2.6   | State machine conventions                                              |      |

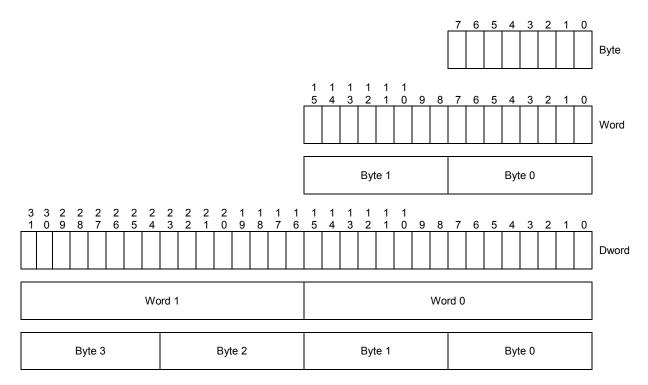

|   | 4.2.7   | Byte, word and Dword Relationships                                     |      |

| 5 |         | overview                                                               | 47   |

| Č |         | itecture                                                               |      |

|   |         | ge Models                                                              |      |

|   | 5.2.1   | Internal 1 meter Cabled Host to Device                                 |      |

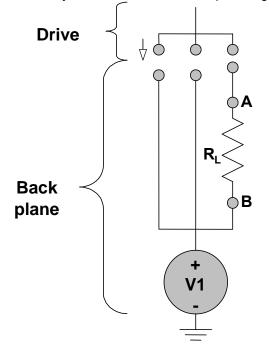

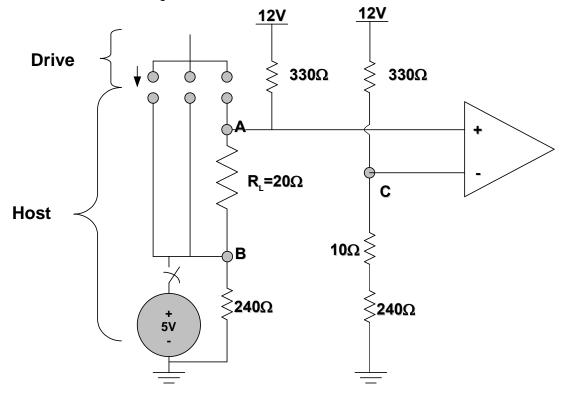

|   | 5.2.2   | Short Backplane to Device                                              |      |

|   | 5.2.3   | Long Backplane to Device                                               |      |

|   | 5.2.4   | Internal 4-lane Cabled Disk Arrays                                     |      |

|   | 5.2.5   | System-to-System Interconnects – Data Center Applications (xSATA)      |      |

|   | 5.2.6   | System-to-System Interconnects – External Desktop Applications (eSATA) |      |

|   | 5.2.7   | Proprietary Serial ATA Disk Arrays                                     |      |

|   | 5.2.8   | Serial ATA and SAS                                                     |      |

|   | 5.2.9   | Potential External SATA Incompatibility Issues                         |      |

|   | 5.2.10  | Mobile Applications                                                    |      |

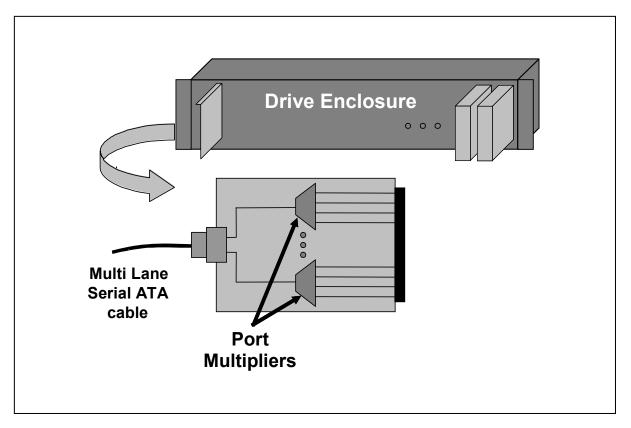

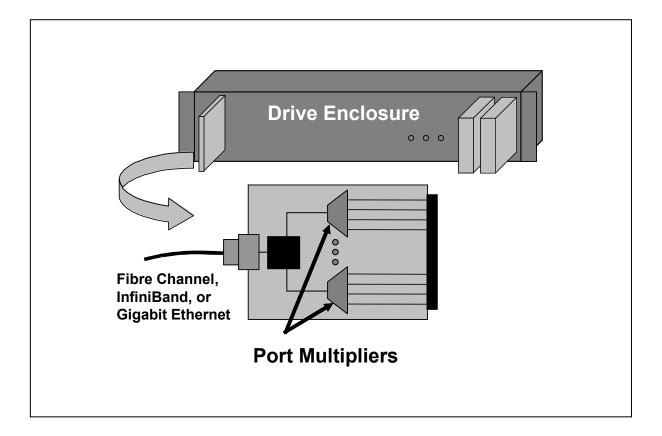

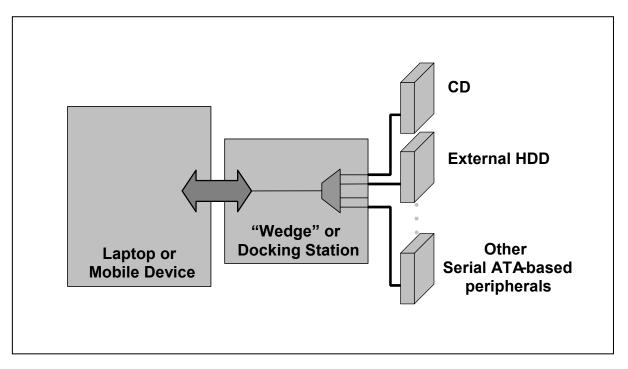

|   | 5.2.11  | Port Multiplier Example Applications                                   |      |

| 6 | •       | and Connectors                                                         |      |

| Ũ |         | nal cables and connectors                                              |      |

|   | 6.1.1   | Internal Single Lane Description                                       |      |

|   | 6.1.2   | Connector locations                                                    |      |

|   | 6.1.3   | Mating interfaces                                                      |      |

|   | 6.1.4   | Signal cable receptacle connector                                      |      |

|   | 6.1.5   | Signal host plug connector                                             |      |

|   | 6.1.6   | Backplane connector                                                    |      |

|   | 6.1.7   | Power cable receptacle connector                                       |      |

|   | 6.1.8   | Internal single lane cable                                             |      |

|   | 6.1.9   | Connector labeling.                                                    |      |

|   | 6.1.10  | Connector and cable assembly requirements and test procedures          |      |

|   | 6.1.11  | Internal Multilane cables                                              |      |

|   | 6.1.12  | Mini SATA Internal Multilane                                           |      |

|   |         | nal Micro SATA Connector for 1.8" HDD                                  | 111  |

|   | 6.2.1   | Usage model                                                            |      |

|   | 6.2.2   | General description                                                    |      |

|   | 6.2.3   | Connector location                                                     |      |

|   | 6.2.4   | Mating interfaces                                                      |      |

|   |         | nal Slimline cables and connectors                                     |      |

|   |         |                                                                        |      |

| 6.3.1    | Usage Models                                                           |         |

|----------|------------------------------------------------------------------------|---------|

| 6.3.2    | General description                                                    |         |

| 6.3.3    | Connector location and keep out zones                                  |         |

| 6.3.4    | Mating interfaces                                                      |         |

| 6.3.5    | Backplane connector configuration and blind-mating tolerance           |         |

| 6.3.6    | Connector labeling                                                     |         |

| 6.3.7    | Connector and cable assembly requirements and test procedures          |         |

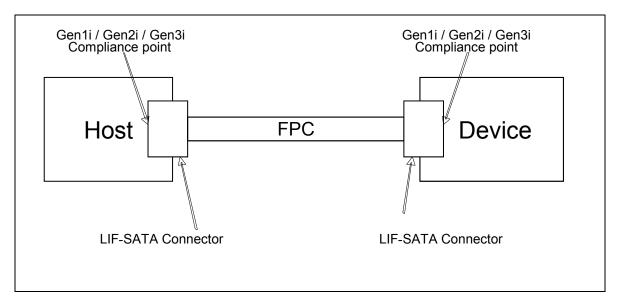

| 6.4 Inte | ernal LIF-SATA Connector for 1.8" HDD                                  | 138     |

| 6.4.1    | General description                                                    | 138     |

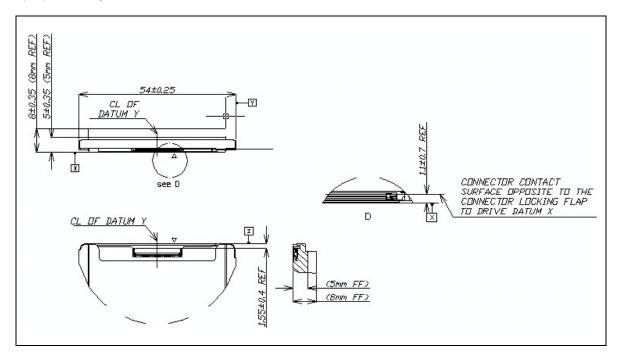

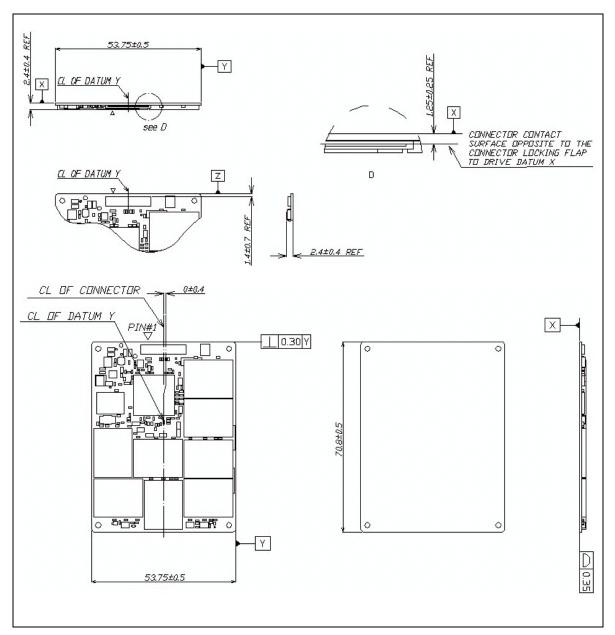

| 6.4.2    | Connector Locations                                                    | 139     |

| 6.4.3    | Mating interfaces                                                      | 141     |

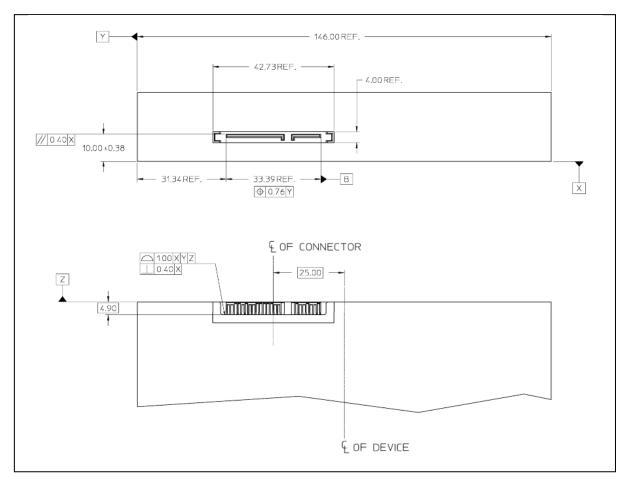

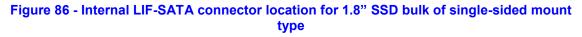

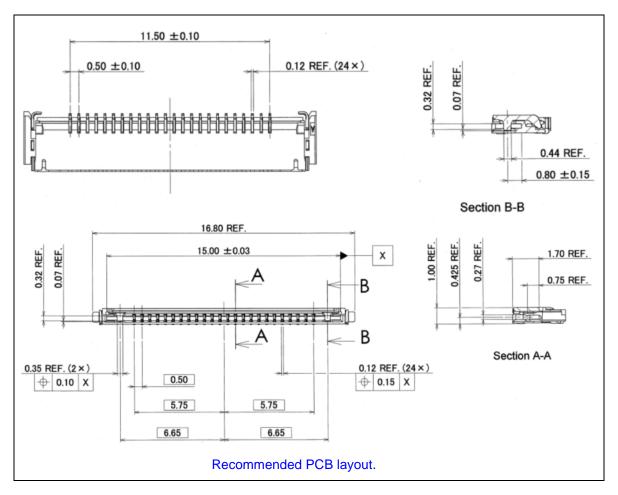

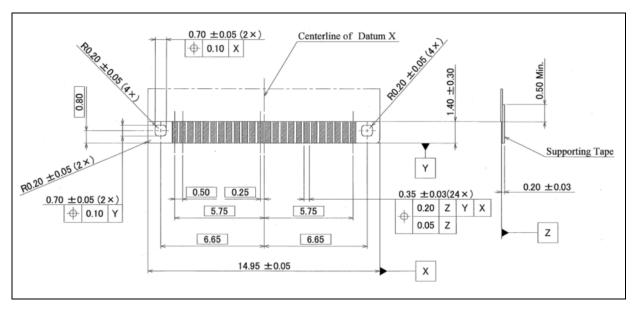

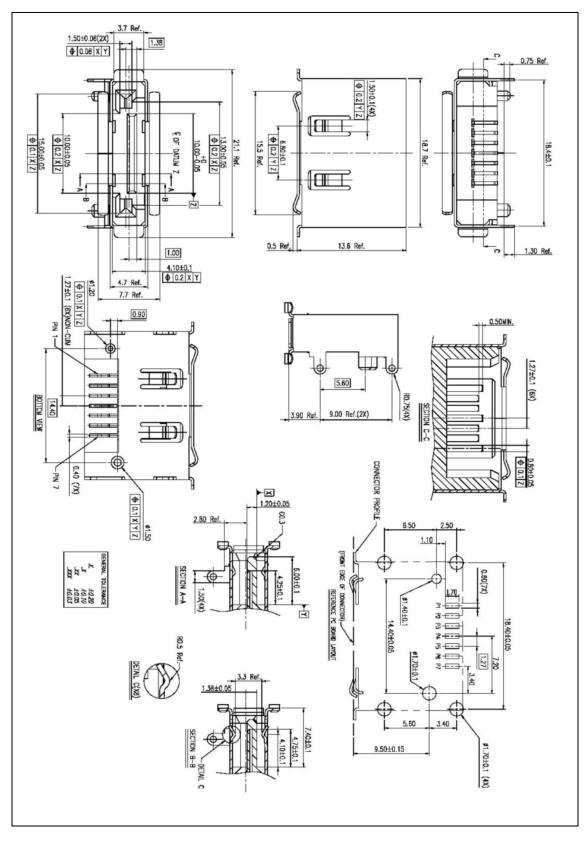

| Figure   | 87 defines the interface dimensions for the internal LIF-SATA embedde  | d type  |

| connect  | or with both signal and power segments.                                | 141     |

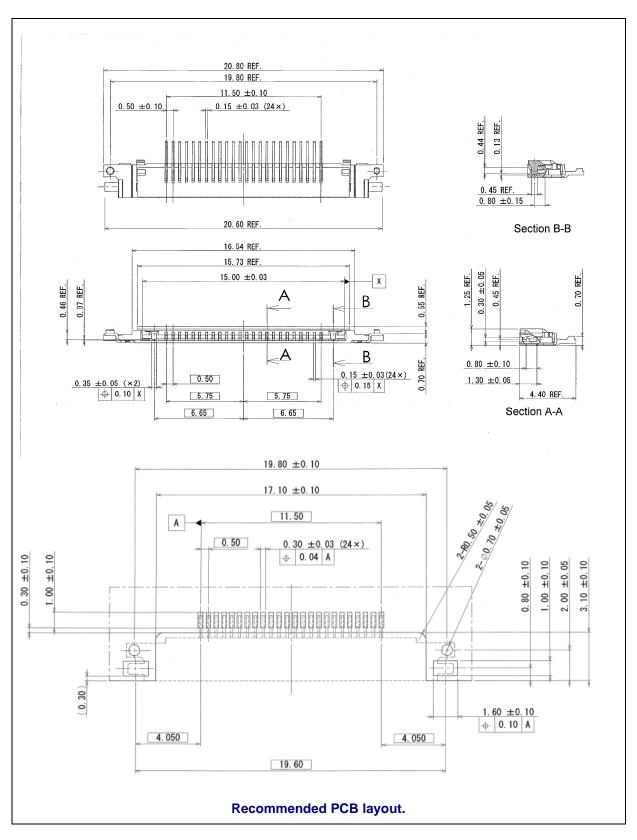

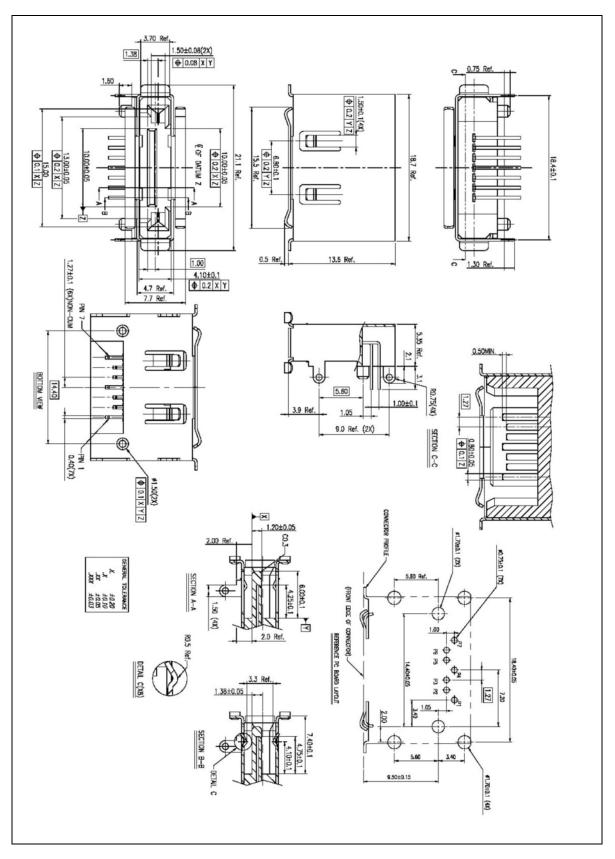

| Figure   | 88 defines the interface dimensions for the internal LIF-SATA device s | surface |

| mountin  | g type connector.                                                      | 143     |

| 6.4.4    | Internal LIF-SATA pin signal definition and contact mating sequence    | 145     |

| 6.4.5    | Housing and contact electrical requirement                             |         |

| 6.5 Ex   | ternal cables and connectors                                           |         |

| 6.5.1    | External Single Lane                                                   | 147     |

| 6.5.2    | External Multilane                                                     | 157     |

| 6.5.3    | Mini SATA External Multilane                                           | 161     |

| 6.6 Ca   | ble and Connector Electrical Specifications                            |         |

| 6.6.1    | Serial ATA Cable                                                       |         |

| 6.6.2    | Cable/Connector Test Methodology                                       |         |

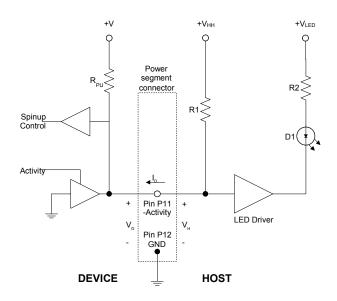

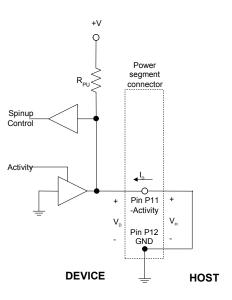

| 6.7 Po   | wer Segment Pin P11 Definition (Optional)                              |         |

| 6.7.1    | Device Activity Signal                                                 |         |

| 6.7.2    | Staggered Spin-up Disable Control                                      |         |

|          | echarge and Device Presence Detection                                  |         |

| 6.8.1    | Device Requirements                                                    |         |

| 6.8.2    | Receptacle Precharge (Informative)                                     |         |

| 6.8.3    | Presence Detection (Informative)                                       |         |

|          | ayer                                                                   |         |

|          | scriptions of Phy Electrical Specifications                            |         |

| 7.1.1    | List of Services                                                       |         |

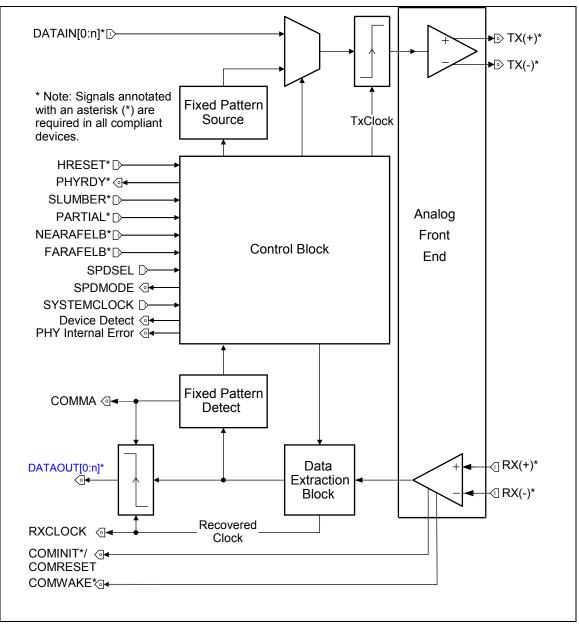

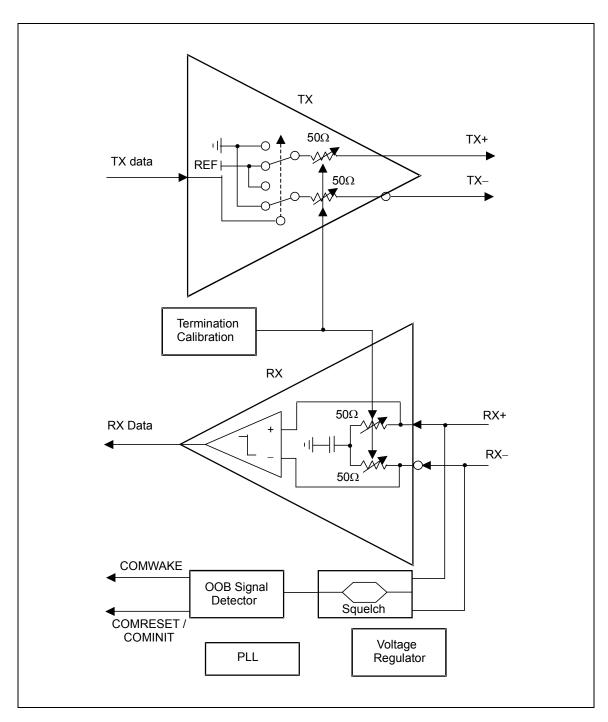

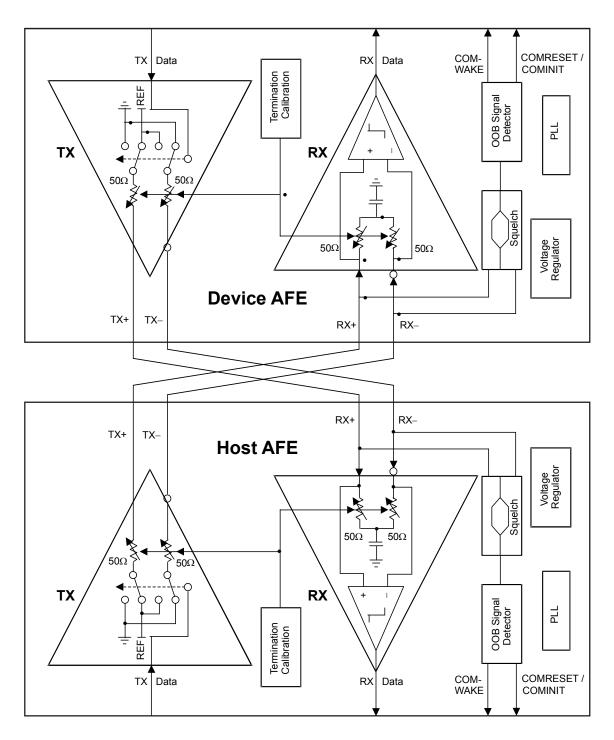

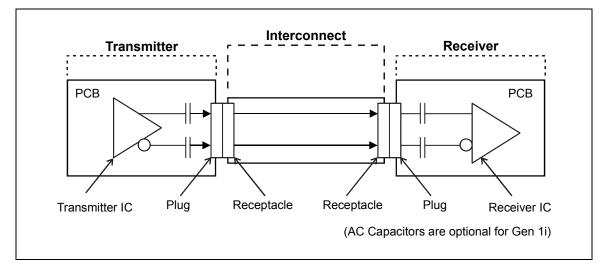

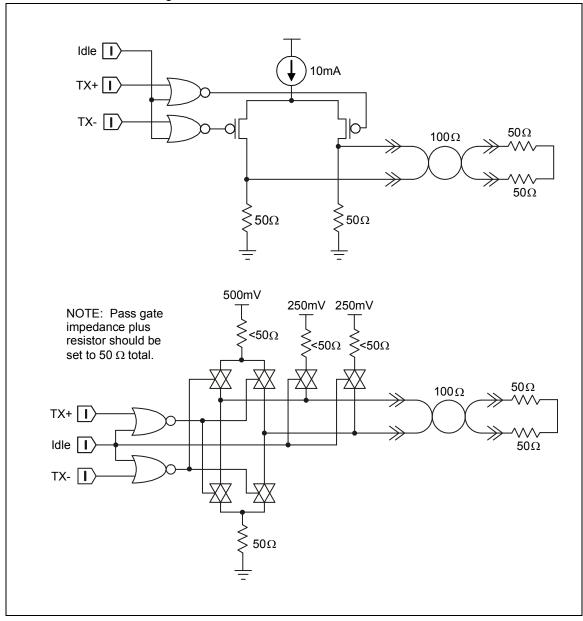

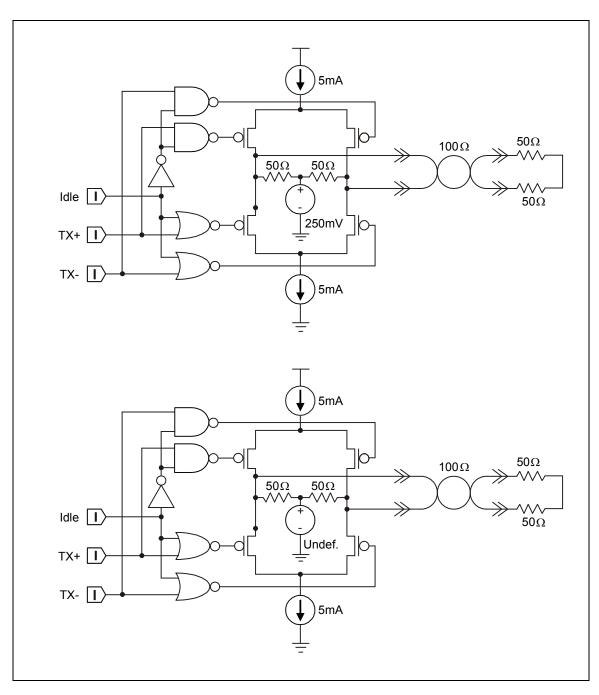

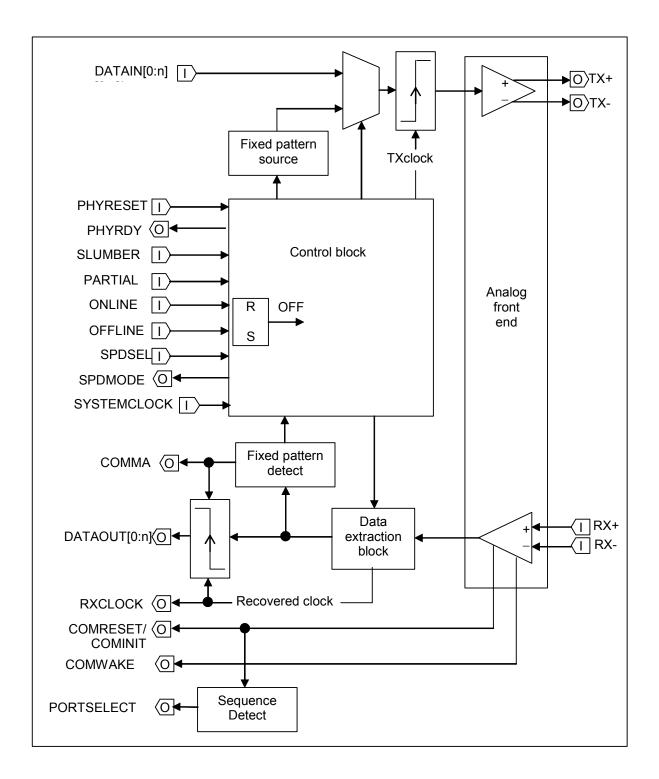

| 7.1.2    | Low Level Electronics Block Diagrams (Informative)                     |         |

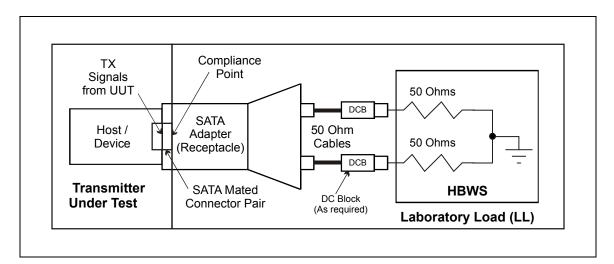

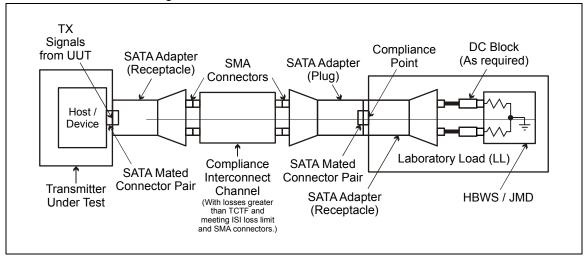

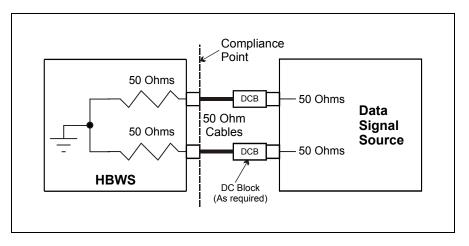

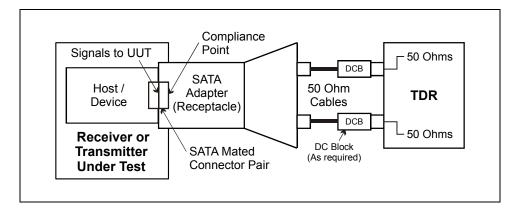

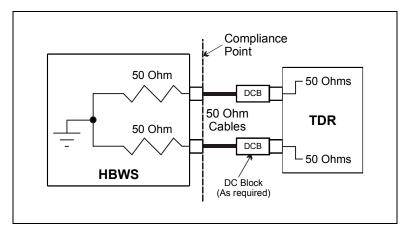

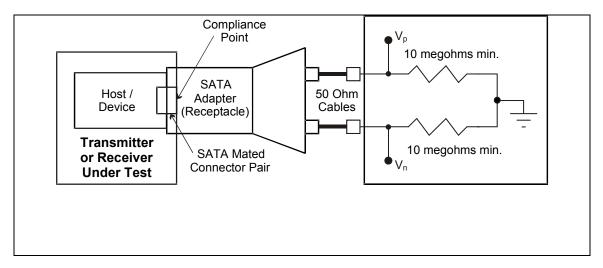

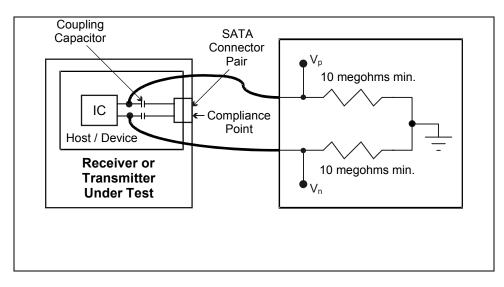

| 7.1.3    | Compliance Testing                                                     |         |

| 7.1.4    | Link Performance                                                       |         |

|          | ectrical Specifications                                                |         |

| 7.2.1    | Physical Layer Requirements Tables                                     |         |

| 7.2.2    | Phy Layer Requirements Details                                         |         |

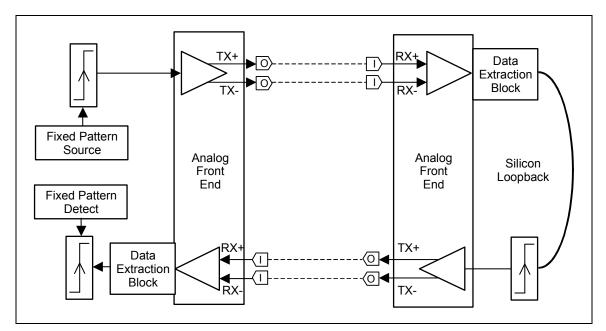

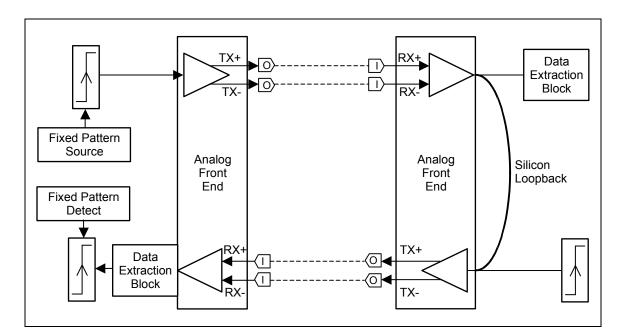

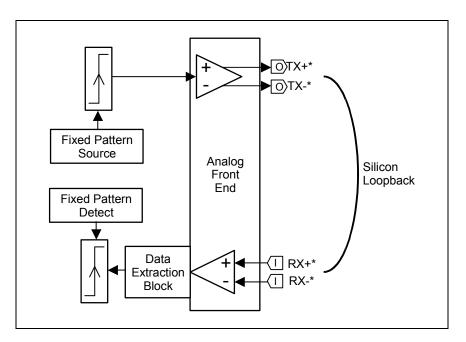

| 7.2.3    | Loopback                                                               |         |

| 7.2.4    | Test Pattern Requirements                                              |         |

| 7.2.5    | Hot Plug Considerations                                                |         |

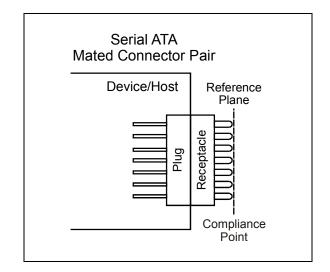

| 7.2.6    | Mated Connector Pair Definition                                        |         |

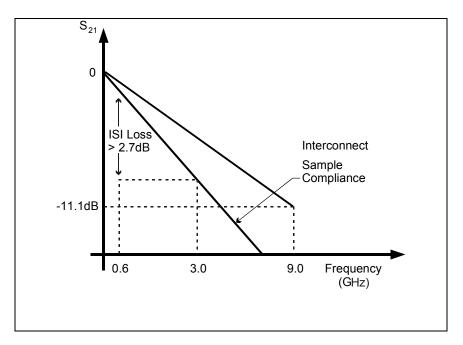

| 7.2.7    | Compliance Interconnect Channels (Gen1x, Gen2x, Gen3i)                 |         |

| 7.2.8    | Impedance Calibration (Optional)                                       |         |

|          | er                                                                     |         |

| 7.3.1    | Jitter Definition                                                      |         |

| 7.3.2    | Reference Clock Definition                                             |         |

| 7.3.3    | Spread Spectrum Clocking                                               |         |

| 7.3.4    | Jitter Budget                                                          |         |

|          | asurements                                                             |         |

| 7.4 We   | Frame Error Rate Testing                                               |         |

| 7.4.1    | Measurement of Differential Voltage Amplitudes (Gen1, Gen2)            |         |

| 7.4.2    | Measurement of Differential Voltage Amplitudes (Gen3i)                 |         |

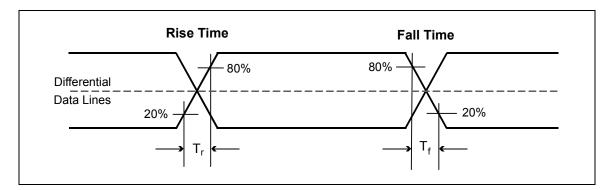

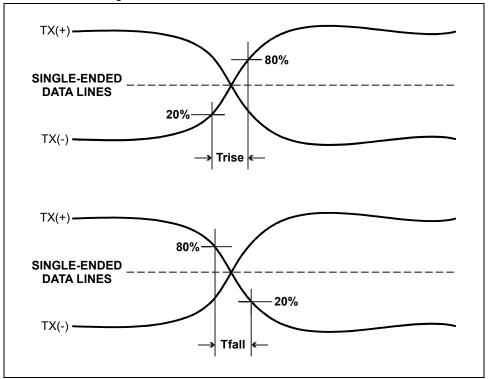

| 7.4.3    | Rise and Fall Times                                                    |         |

| 1.4.4    |                                                                        | 210     |

|   | 7.4.5    | Transmitter Amplitude                                             |       |

|---|----------|-------------------------------------------------------------------|-------|

|   | 7.4.6    | Receive Amplitude                                                 |       |

|   | 7.4.7    | Long Term Frequency Accuracy                                      |       |

|   | 7.4.8    | Jitter Measurements                                               |       |

|   | 7.4.9    | Transmit Jitter (Gen1i, Gen2i, Gen1m, Gen2m, Gen1x, and Gen2x)    |       |

|   | 7.4.10   | Transmit Jitter (Gen3i)                                           |       |

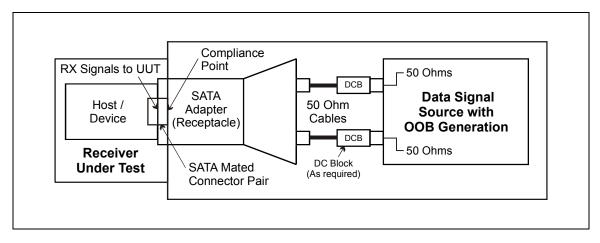

|   | 7.4.11   | Receiver Tolerance (Gen1i, Gen2i, Gen1m, Gen2m, Gen1x, and Gen2x) | . 290 |

|   | 7.4.12   | Receiver Tolerance (Gen3i)                                        | . 292 |

|   | 7.4.13   | Return Loss and Impedance Balance                                 |       |

|   | 7.4.14   | SSC Profile                                                       | . 298 |

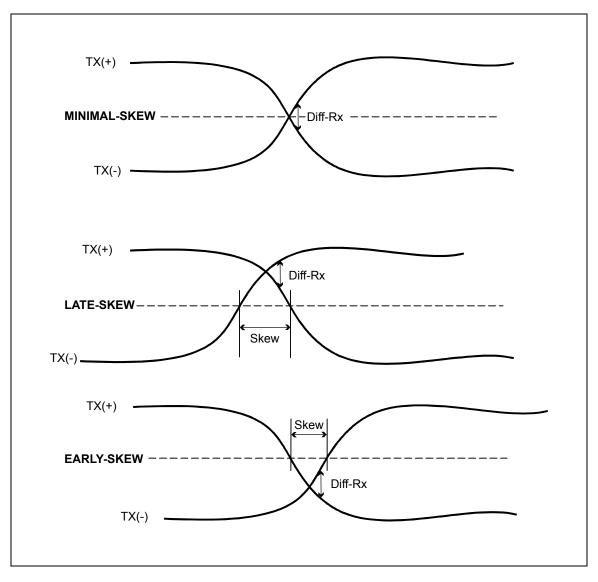

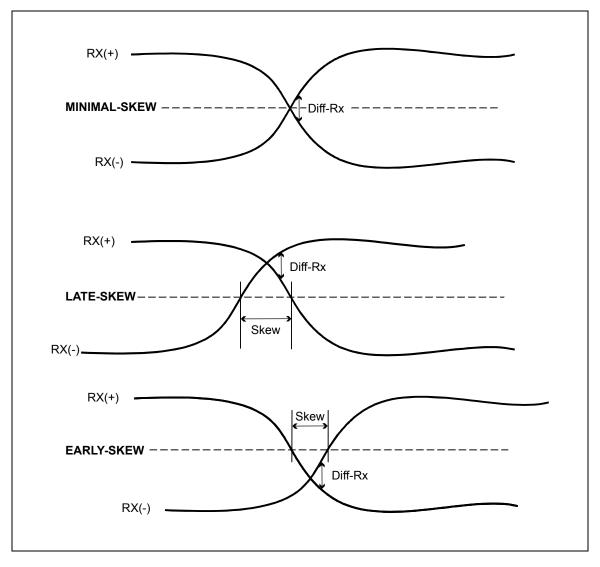

|   | 7.4.15   | Intra-Pair Skew                                                   | . 298 |

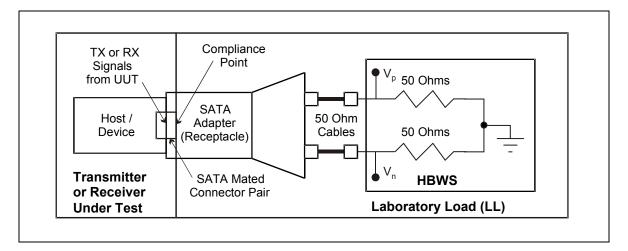

|   | 7.4.16   | Sequencing Transient Voltage                                      | . 300 |

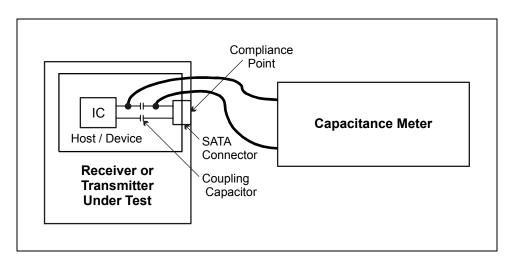

|   | 7.4.17   | AC Coupling Capacitor                                             |       |

|   | 7.4.18   | TX Amplitude Imbalance                                            |       |

|   | 7.4.19   | TX Rise/Fall Imbalance                                            |       |

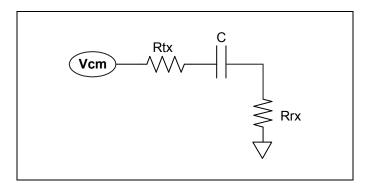

|   | 7.4.20   | TX AC Common Mode Voltage (Gen2i, Gen2m)                          |       |

|   | 7.4.21   | Tx AC Common Mode Voltage (Gen3i)                                 |       |

|   | 7.4.22   | OOB Common Mode Delta                                             |       |

|   | 7.4.23   | OOB Differential Delta                                            |       |

|   | 7.4.24   | Squelch Detector Tests                                            |       |

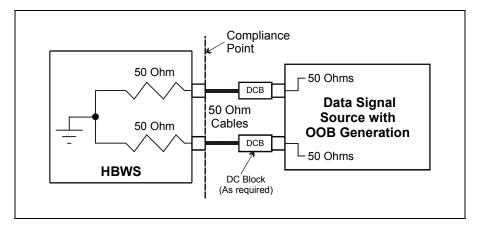

|   | 7.4.25   | OOB Signaling Tests                                               |       |

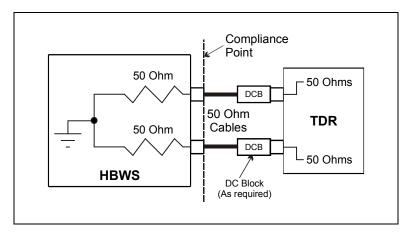

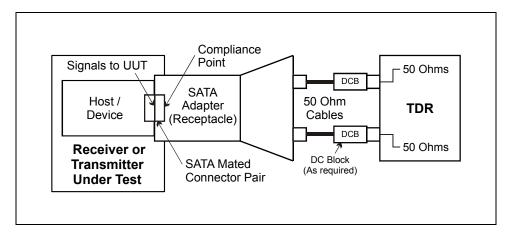

|   | 7.4.25   | TDR Differential Impedance (Gen1i / Gen1m)                        |       |

|   | 7.4.20   | TDR Single-Ended Impedance (Gen1i / Gen1m)                        |       |

|   | 7.4.27   | DC Coupled Common Mode Voltage (Gen1i / Gen1m)                    |       |

|   |          |                                                                   |       |

|   | 7.4.29   | AC Coupled Common Mode Voltage (Gen1i / Gen1m)                    |       |

|   | 7.4.30   | Sequencing Transient Voltage - Laboratory Load (Gen3i)            |       |

|   |          | face States                                                       |       |

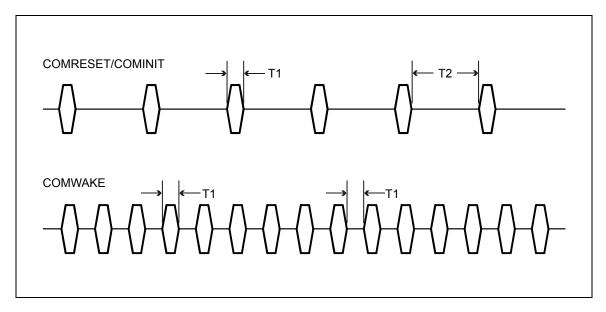

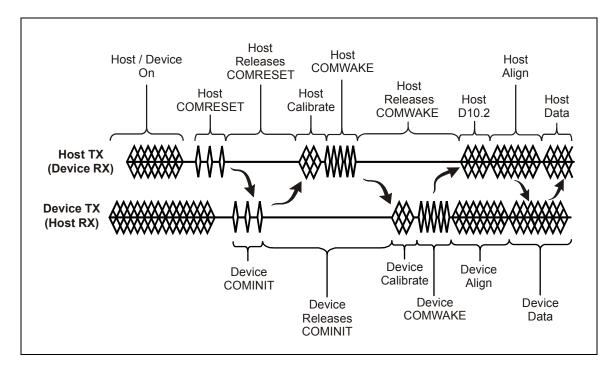

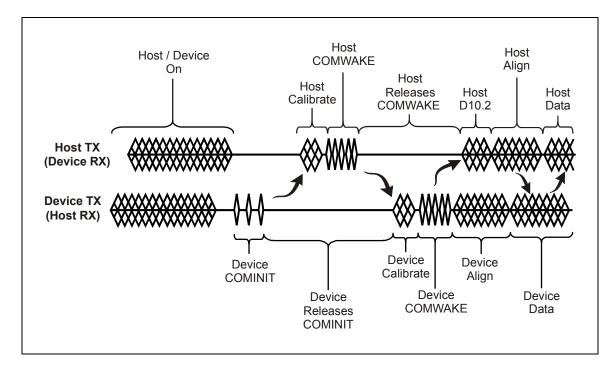

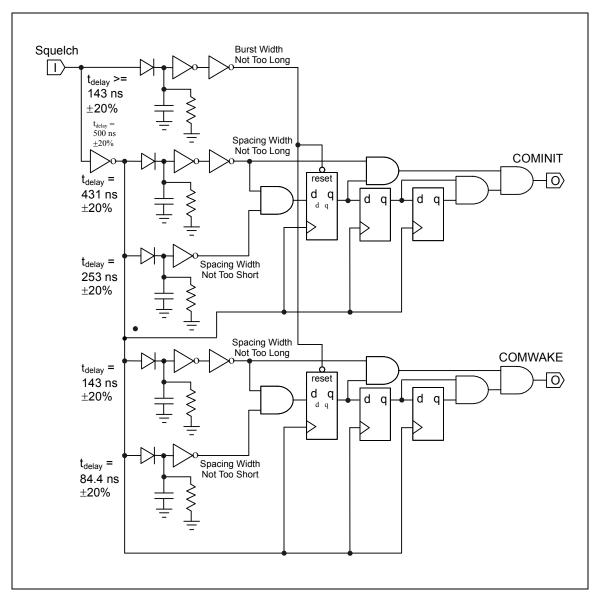

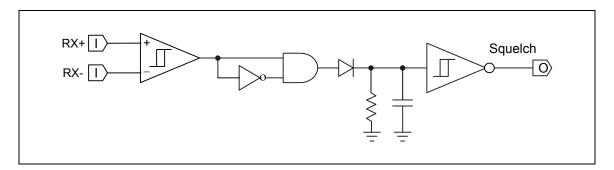

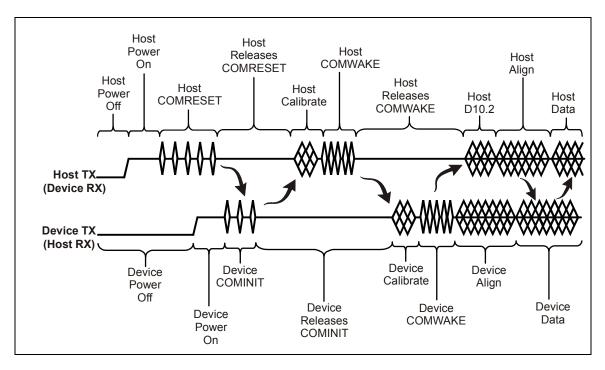

|   | 7.5.1    | Out Of Band Signaling                                             |       |

|   | 7.5.2    | Idle Bus Condition                                                |       |

| _ |          | ticity Buffer Management                                          |       |

| 8 |          | d Phy Power States                                                |       |

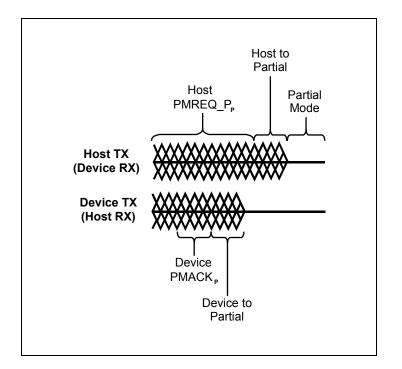

|   |          | face Power States                                                 |       |

|   |          | nchronous Signal Recovery (Optional)                              |       |

|   | 8.2.1    | Unsolicited COMINIT Usage (Informative)                           | . 319 |

|   |          | 3 and Signature FIS return (Informative)                          |       |

|   | 8.4 Pow  | er-On Sequence State Machine                                      |       |

|   | 8.4.1    | Host Phy Initialization State Machine                             |       |

|   | 8.4.2    | Device Phy Initialization State Machine                           |       |

|   | 8.4.3    | Speed Negotiation                                                 | . 329 |

| 9 | Link Lay | /er                                                               | 335   |

|   | 9.1 Ove  | rview                                                             | . 335 |

|   | 9.1.1    | Frame Transmission                                                | . 335 |

|   | 9.1.2    | Frame Reception                                                   | . 335 |

|   | 9.2 Enco | oding Method                                                      | . 335 |

|   | 9.2.1    | Notation and Conventions                                          | . 336 |

|   | 9.2.2    | Character Code                                                    | . 337 |

|   | 9.2.3    | Transmission Summary                                              | . 345 |

|   | 9.2.4    | Reception Summary                                                 |       |

|   | 9.3 Tran | nsmission Overview                                                |       |

|   |          | itives                                                            |       |

|   | 9.4.1    | Overview                                                          |       |

|   | 9.4.2    | Primitive Descriptions                                            |       |

|   | 9.4.3    | Primitive Encoding                                                |       |

|   | 9.4.4    | DMAT <sub>P</sub> Primitive                                       |       |

|   | 9.4.5    | CONT <sub>P</sub> Primitive                                       |       |

|   | 9.4.6    | ALIGN <sub>P</sub> Primitive                                      |       |

|   |          |                                                                   |       |

| 9.4.7      | Flow Control Signaling Latency                                           |       |

|------------|--------------------------------------------------------------------------|-------|

| 9.4.8      | Examples of Primitive Usage (Informative)                                |       |

| 9.5 CRC    | and Scrambling                                                           |       |

| 9.5.1      | Relationship Between Scrambling of FIS Data and Repeated Primitives      |       |

| 9.5.2      | Relationship Between Scrambling and CRC                                  |       |

| 9.5.3      | Scrambling Disable (Informative)                                         | . 359 |

| 9.6 Link   | Layer State Machine                                                      | . 359 |

| 9.6.1      | Terms Used in Link Layer Transition Tables                               |       |

| 9.6.2      | Link Idle State Diagram                                                  |       |

| 9.6.3      | Link Transmit State Diagram                                              |       |

| 9.6.4      | Link Receive State Diagram                                               |       |

| 9.6.5      | Link Power Mode State Diagram                                            |       |

| 10 Transpo | rt Layer                                                                 |       |

|            | rview                                                                    |       |

| 10.1.1     | FIS construction                                                         |       |

| 10.1.2     | FIS decomposition                                                        |       |

|            | ne Information Structure (FIS)                                           |       |

| 10.2.1     | Overview                                                                 |       |

| 10.2.1     |                                                                          |       |

|            | Payload content                                                          |       |

| 10.3 FIS   | Types                                                                    |       |

|            | FIS Type values<br>CRC Errors on Data FISes                              |       |

| 10.3.2     |                                                                          |       |

| 10.3.3     | All FIS types                                                            |       |

| 10.3.4     | Register - Host to Device                                                |       |

| 10.3.5     | Register - Device to Host                                                | . 386 |

| 10.3.6     | Set Device Bits - Device to Host                                         |       |

| 10.3.7     | DMA Activate - Device to Host                                            |       |

| 10.3.8     | DMA Setup – Device to Host or Host to Device (Bidirectional)             |       |

| 10.3.9     | BIST Activate - Bidirectional                                            |       |

| 10.3.10    | PIO Setup – Device to Host                                               |       |

| 10.3.11    | Data - Host to Device or Device to Host (Bidirectional)                  |       |

| 10.4 Host  | transport states                                                         |       |

| 10.4.1     | Host transport idle state diagram                                        | . 399 |

| 10.4.2     | Host Transport transmit command FIS diagram                              | . 402 |

| 10.4.3     | Host Transport transmit control FIS diagram                              | . 403 |

| 10.4.4     | Host Transport transmit DMA Setup – Device to Host or Host to Device FIS |       |

| diagram    | 404                                                                      |       |

| 10.4.5     | Host Transport transmit BIST Activate FIS                                | . 405 |

| 10.4.6     | Host Transport decomposes Register FIS diagram                           |       |

| 10.4.7     | Host Transport decomposes a Set Device Bits FIS state diagram            |       |

| 10.4.8     | Host Transport decomposes a DMA Activate FIS diagram                     |       |

| 10.4.9     | Host Transport decomposes a PIO Setup FIS state diagram                  |       |

| 10.4.10    | Host Transport decomposes a DMA Setup FIS state diagram                  |       |

| 10.4.11    | Host transport decomposes a BIST Activate FIS state diagram              |       |

|            | ce transport states                                                      |       |

| 10.5.1     | Device transport idle state diagram                                      | 416   |

| 10.5.2     | Device Transport sends Register – Device to Host state diagram           |       |

| 10.5.3     | Device Transport sends Set Device Bits FIS state diagram                 |       |

| 10.5.3     | Device Transport transmit PIO Setup – Device to Host FIS state diagram   |       |

| 10.5.4     |                                                                          |       |

|            | Device Transport transmit DMA Activate FIS state diagram                 |       |

| 10.5.6     | Device Transport transmit DMA Setup – Device to Host FIS state diagram   |       |

| 10.5.7     | Device Transport transmit Data – Device to Host FIS diagram.             |       |

| 10.5.8     | Device Transport transmit BIST Activate FIS diagram                      |       |

| 10.5.9     | Device Transport decomposes Register – Host to Device state diagram      |       |

| 10.5.10    | Device Transport decomposes Data (Host to Device) FIS state diagram      |       |

| 10.5.11    | Device Transport decomposes DMA Setup – Host to Device state diagram     | . 427 |

| 10.5.12           | Device Transport decomposes a BIST Activate FIS state diagram     | 428 |

|-------------------|-------------------------------------------------------------------|-----|

|                   | Command Layer protocol                                            |     |

|                   | wer-on and COMRESET protocol                                      |     |

|                   | vice Idle protocol                                                |     |

|                   | ftware reset protocol                                             |     |

|                   | ECUTE DEVICE DIAGNOSTIC command protocol                          |     |

| 11.5 DE           | VICE RESET command protocol                                       | 442 |

|                   | n-data command protocol                                           |     |

|                   | D data-in command protocol                                        |     |

| 11.8 PI           | D data-out command protocol                                       | 445 |

|                   | IA data in command protocol                                       |     |

| 11.10             | DMA data out command protocol                                     | 447 |

|                   | PACKET protocol                                                   |     |

| 11.12             | READ DMA QUEUED command protocol                                  | 454 |

| 11.13             | WRITE DMA QUEUED command protocol                                 | 456 |

| 11.14             | FPDMA QUEUED command protocol                                     | 458 |

|                   | ommand Layer protocol                                             |     |

|                   | DMA QUEUED command protocol                                       |     |

|                   | ation Layer                                                       |     |

|                   | rallel ATA Emulation                                              |     |

| 13.1.1            | Software Reset                                                    |     |

| 13.1.2            | Master-only emulation                                             |     |

| 13.1.3            | Master/Slave emulation (optional)                                 |     |

|                   | ENTIFY (PACKET) DEVICE                                            |     |

| 13.2.1            | IDENTIFY DEVICE                                                   | 475 |

| 13.2.1            | IDENTIFY PACKET DEVICE                                            | 473 |

| 13.2.2            | Determining Support for Serial ATA Features                       | 407 |

|                   | T FEATURES                                                        |     |

| 13.3 SE<br>13.3.1 |                                                                   |     |

|                   | Enable/Disable Non-Zero Offsets in DMA Setup                      |     |

| 13.3.2            | Enable/Disable DMA Setup FIS Auto-Activate Optimization           |     |

| 13.3.3            | Enable/Disable Device-Initiated Interface Power State Transitions |     |

| 13.3.4            | Enable/Disable Guaranteed in-Order Data Delivery                  |     |

| 13.3.5            | Enable/Disable Asynchronous Notification                          |     |

| 13.3.6            | Enable/Disable Software Settings Preservation                     |     |

| 13.3.7            | Enable/Disable Device Automatic Partial to Slumber Transitions    |     |

|                   | vice Configuration Overlay                                        |     |

| 13.4.1            | Device Configuration Overlay Identify                             |     |

| 13.4.2            | Device Configuration Overlay Set                                  |     |

|                   | ftware Settings Preservation (Optional)                           |     |

| 13.5.1            | Warm Reboot Considerations (Informative)                          |     |

| 13.6 Na           | tive Command Queuing (Optional)                                   | 498 |

| 13.6.1            | Definition                                                        |     |

| 13.6.2            | Intermixing Non-Native Queued Commands and Native Queued Commands | 503 |

| 13.6.3            | Command Definitions                                               |     |

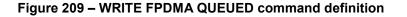

| 13.6.4            | First-party DMA HBA Support (Informative)                         | 522 |

| 13.7 SA           | TA Logs                                                           |     |

| 13.7.1            | Log Address Definitions                                           |     |

| 13.7.2            | General Purpose Log Directory (00h)                               |     |

| 13.7.3            | Queued Error Log (10h)                                            |     |

| 13.7.4            | Phy Event Counters Log (11h)                                      | 526 |

| 13.7.5            | NCQ Queue Management Log (12h)                                    | 526 |

|                   | ynchronous Notification (Optional)                                | 527 |

| 13.8.1            | Set Device Bits FIS Notification bit                              | 527 |

| 13.8.2            | Notification Mechanism                                            |     |

| 13.8.3            | State Diagram for Asynchronous Notification                       |     |

| 13.8.4            | ATAPI Notification                                                |     |

| 10.0.7            |                                                                   | 520 |

| 13.9 Pł    | ny Event Counters (Optional)                                       | 528 |

|------------|--------------------------------------------------------------------|-----|

| 13.9.1     | Counter Reset Mechanisms                                           | 529 |

| 13.9.2     | Counter Identifiers                                                | 529 |

| 13.9.3     | Phy Event Counters Log (11h)                                       |     |

|            | Staggered Spin-up (Optional)                                       |     |

| 13.11      | Non-512 Byte Sector Size (Informative)                             | 533 |

| 13.12      | Defect Management (Informative)                                    | 534 |

| 13.12.1    |                                                                    |     |

| 13.12.2    | 2 Typical Serial ATA Reliability Metrics (Informative)             | 534 |

| 13.12.3    | <b>0</b> ( )                                                       |     |

| 13.12.4    |                                                                    |     |

| 13.12.5    | 5 Self-Monitoring, Analysis and Reporting Technology (Informative) | 535 |

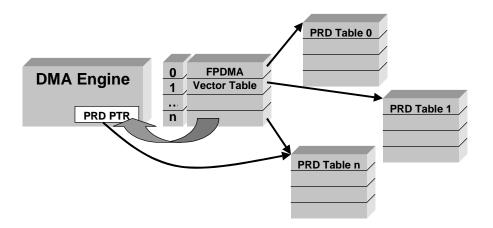

| 13.13      | Enclosure Services/Management (Optional)                           |     |

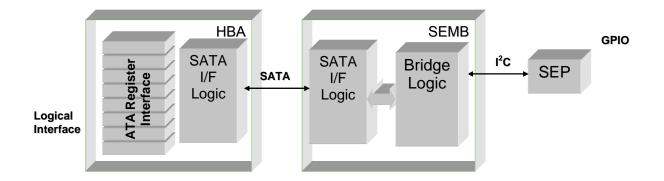

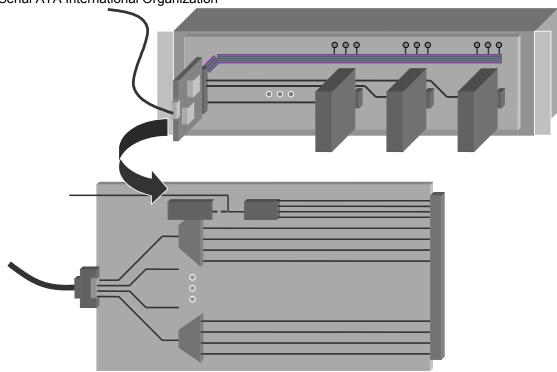

| 13.13.1    | Overview                                                           | 536 |

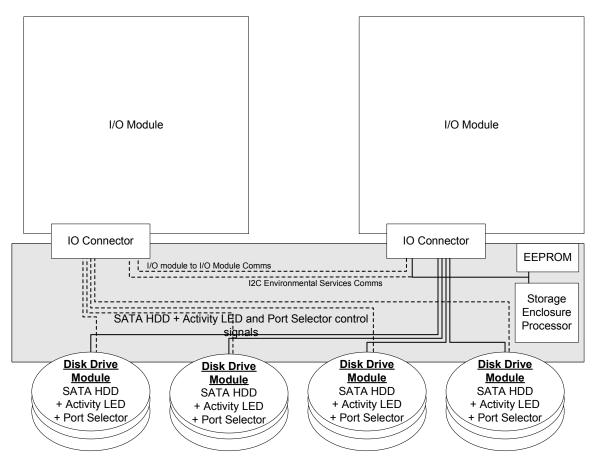

| 13.13.2    | 2 Topology                                                         | 536 |

| 13.13.3    | Limitations                                                        | 538 |

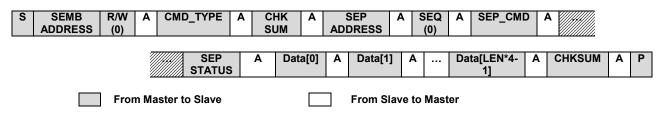

| 13.13.4    | Definition                                                         | 538 |

| 13.13.5    | 5 SES and SAF-TE Extensions                                        | 544 |

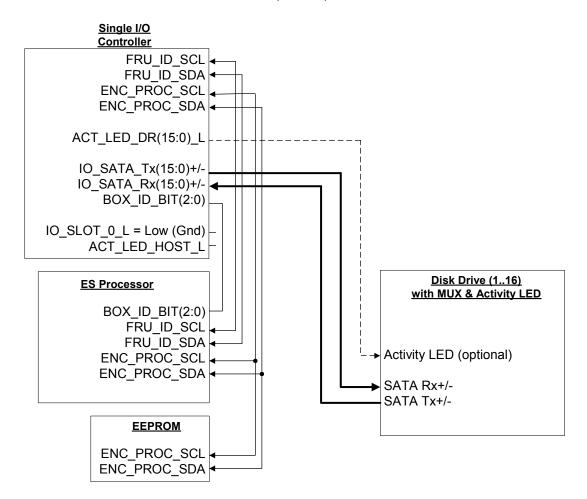

| 13.13.6    | Enclosure Services Hardware Interface                              | 550 |

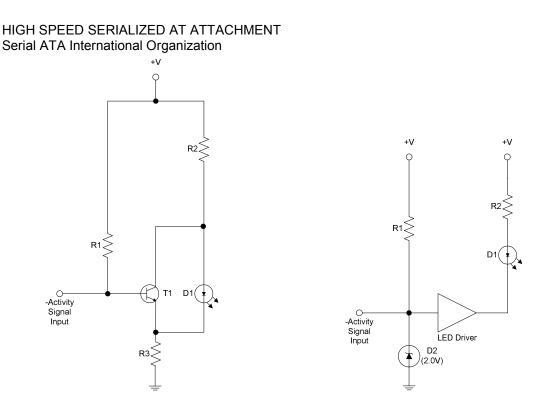

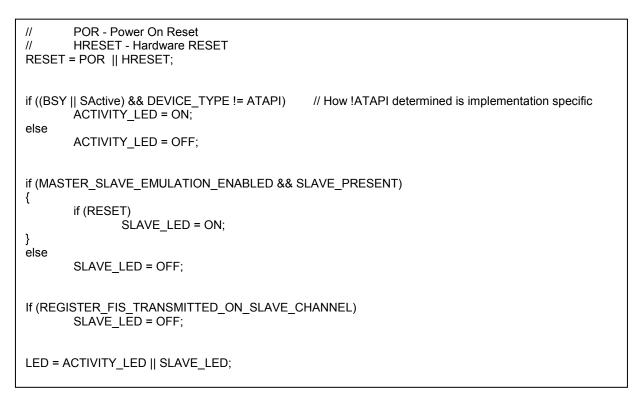

| 13.14      | HDD Activity Indication (Optional)                                 | 551 |

| 13.14.1    | HDD Activity Emulation of Desktop Behavior                         | 551 |

| 13.14.2    |                                                                    |     |

| 13.15      | Port Multiplier Discovery and Enumeration                          | 555 |

| 13.15.1    |                                                                    |     |

| 13.15.2    | Resets                                                             | 556 |

| 13.15.3    | Software Initialization Sequences (Informative)                    | 557 |

| 13.15.4    | Port Multiplier Discovery and Device Enumeration (Informative)     | 557 |

| 13.16      | Automatic Partial to Slumber Transitions                           |     |

| 14 Host a  | adapter register interface                                         | 560 |

| 14.1 St    | atus and Control Registers                                         | 560 |

| 14.1.1     | SStatus register                                                   | 561 |

| 14.1.2     | SError register                                                    | 561 |

| 14.1.3     | SControl register                                                  | 563 |

| 14.1.4     | SActive register                                                   |     |

| 14.1.5     | SNotification register (Optional)                                  | 565 |

| 15 Error l | handling                                                           | 567 |

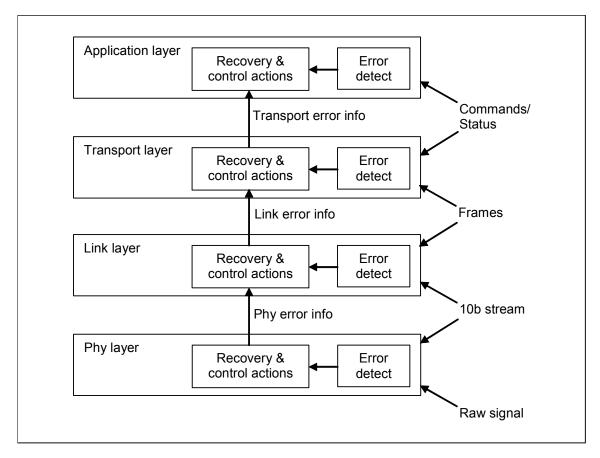

| 15.1 Ar    | chitecture                                                         | 567 |

| 15.2 Pł    | ny error handling overview                                         | 568 |

| 15.2.1     | Error detection                                                    | 568 |

| 15.2.2     | Error control actions                                              | 569 |

| 15.2.3     | Error reporting                                                    |     |

| 15.3 Lir   | nk layer error handling overview                                   | 570 |

| 15.3.1     | Error detection                                                    | 570 |

| 15.3.2     | Error control actions                                              | 570 |

| 15.3.3     | Error reporting                                                    |     |

| 15.4 Tr    | ansport layer error handling overview                              | 571 |

| 15.4.1     | Error detection                                                    |     |

| 15.4.2     | Error control actions                                              | 572 |

| 15.4.3     | Error reporting                                                    | 573 |

| 15.5 Ap    | oplication layer error handling overview                           |     |

| 15.5.1     | Error detection                                                    |     |

| 15.5.2     | Error control actions                                              | 574 |

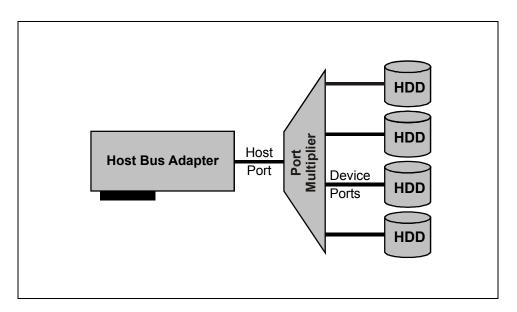

| 16 Port M  | 1ultiplier                                                         | 577 |

| 16.1 Int   | roduction                                                          | 577 |

| 16.2 Ov    | /erview                                                            | 577 |

| 16.3 De    | efinition                                                          | 578 |

|            |                                                                    |     |

| 16.3        |       | Addressing Mechanism                                       |             |

|-------------|-------|------------------------------------------------------------|-------------|

| 16.3        |       | Device Port Requirements                                   |             |

| 16.3        |       | Policies                                                   |             |

|             |       | Multiplier Registers                                       |             |

| 16.4        |       | General Status and Control Registers                       |             |

| 16.4        |       | Port Status and Control Registers                          |             |

|             |       | Multiplier Command Definitions                             |             |

| 16.5        |       | READ PORT MULTIPLIER                                       |             |

| 16.5        |       | WRITE PORT MULTIPLIER                                      |             |

| 16.5        |       | Interrupts                                                 | 604         |

| 16.6        |       | rolling PM Port Value and Interface Power Management       |             |

| 16.7        |       | ching Types (Informative)                                  |             |

| 16.7        |       | Command-Based Switching                                    |             |

|             |       | FIS-Based Switching                                        |             |

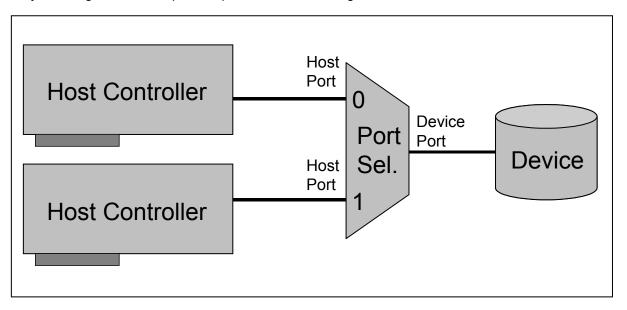

|             |       | ector                                                      |             |

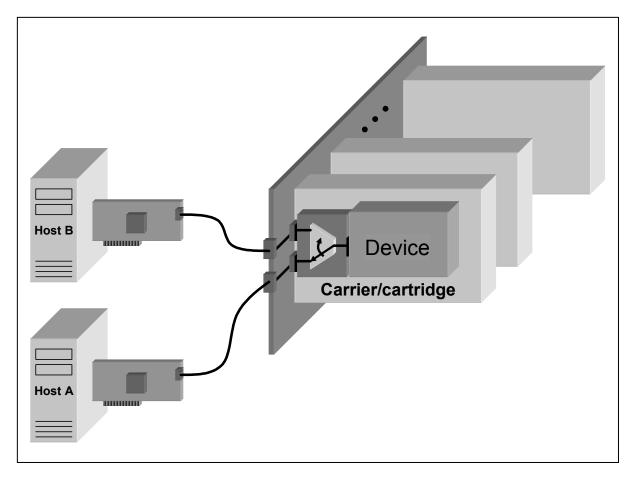

| 17.1        | Exar  | nple Applications                                          | 607         |

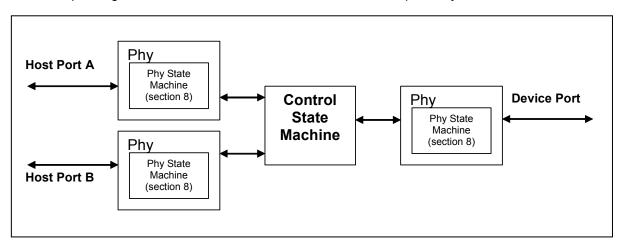

| 17.2        |       | rview                                                      |             |

| 17.3        | Activ | e Port Selection                                           | 609         |

| 17.3        | .1    | Protocol-based Port Selection                              | 609         |

| 17.3        | .2    | Side-band Port Selection                                   | 612         |

| 17.3        | .3    | Behavior during a change of active port                    | 612         |

| 17.4        | Beha  | avior and Policies                                         | 613         |

| 17.4        | .1    | Control State Machine                                      | 613         |

| 17.4        | .2    | BIST support                                               | 617         |

| 17.4        | .3    | Flow control signaling latency                             | 617         |

| 17.4        | .4    | Power Management                                           | 617         |

| 17.4        | .5    | OOB Phy signals                                            |             |

| 17.4        | .6    | Hot Plug                                                   |             |

| 17.4        | .7    | Speed Negotiation                                          | 618         |

| 17.4        | .8    | Spread spectrum clocking                                   | 619         |

| 17.5        | Pow   | er-up and Resets                                           | 619         |

| 17.5        | .1    | Power-up                                                   | 619         |

| 17.5        | .2    | Resets                                                     | 619         |

| 17.6        | Host  | Implementation (Informative)                               |             |

| 17.6        |       | Software Method for Protocol-based Selection (Informative) |             |

| Appendix    | Α.    | Sample Code for CRC and Scrambling (Informative)           |             |

| A.1         |       | calculation                                                |             |

| A.1.1       |       | Overview                                                   |             |

| A.1.2       | 2     | Maximum frame size                                         | 623         |

| A.1.3       | 3     | Example code for CRC algorithm                             |             |

| A.1.4       |       | Example code for CRC algorithm                             |             |

| A.1.5       | 5     | Example CRC implementation output                          |             |

| A.2         |       | mbling calculation                                         |             |

| A.2.1       |       | Overview                                                   |             |

| A.2.2       | 2     | Example code for scrambling algorithm                      |             |

| A.2.3       |       | Example scrambler implementation                           |             |

| A.2.4       |       | Example scrambler implementation output                    |             |

| A.3         |       | nple frame                                                 |             |

| Appendix    |       | Command processing overview (Informative)                  |             |

| B.1         |       | -data commands                                             |             |

| B.2         |       | A read by host from device                                 |             |

| B.3         |       | A write by host to device                                  |             |

| B.4         |       | data read from the device                                  |             |

| B.5         |       | data write to the device                                   |             |

| B.6         |       | Tagged Command Queuing DMA read from device                |             |

| B.7         |       | Tagged Command Queuing DMA read norm device                |             |

| <b>D</b> ., |       |                                                            | <b>JJ</b> ( |

| B.8      | ATAPI Packet commands with PIO data in             |     |

|----------|----------------------------------------------------|-----|

| B.9      | ATAPI Packet commands with PIO data out            | 635 |

| B.10     | ATAPI Packet commands with DMA data in             |     |

| B.11     | ATAPI Packet commands with DMA data out            | 637 |

| B.12     | Odd word count considerations                      |     |

| B.12     | 2.1 DMA read from target for odd word count        | 638 |

| B.12     | 2.2 DMA write by host to target for odd word count |     |

| B.13     | PIO data read from the device                      | 639 |

| B.14     | PIO data write to the device                       |     |

| B.15     | Native Command Queuing Examples (Informative)      |     |

| B.15     | 5.1 Queued Commands with Out of Order Completion   | 640 |

| B.15     |                                                    |     |

| Appendix |                                                    |     |

| Appendix |                                                    |     |

|          | Supported Configurations                           |     |

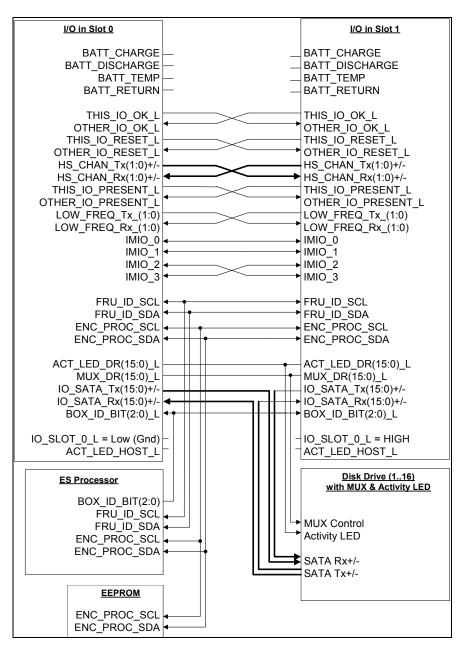

| D.1.     |                                                    |     |

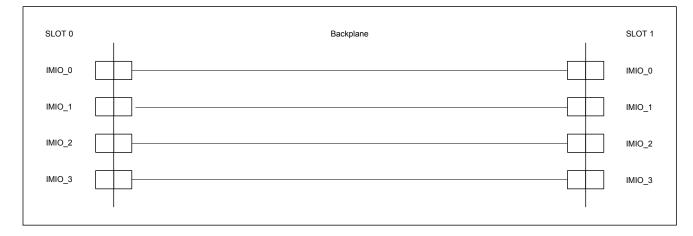

|          | 2 Dual I/O Controller Signals                      |     |

| D.1.     |                                                    |     |

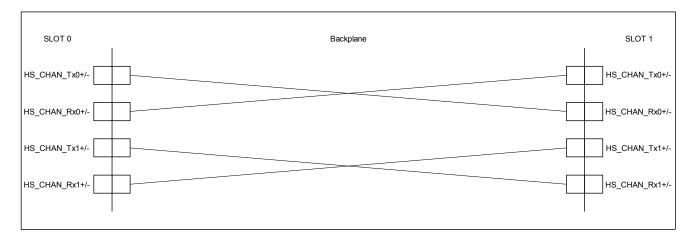

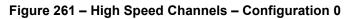

| D.2      | Optional High Speed Channel configurations         |     |

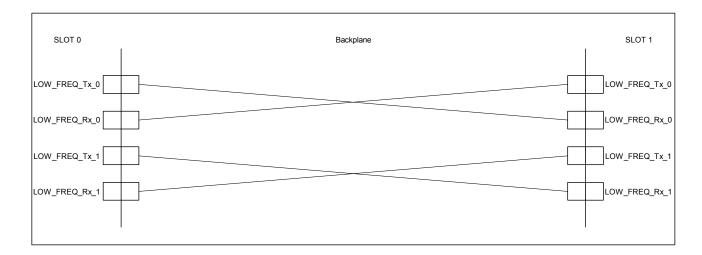

| D.3      | Optional Low Speed Channel configurations          |     |

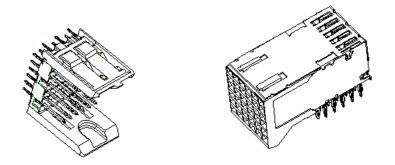

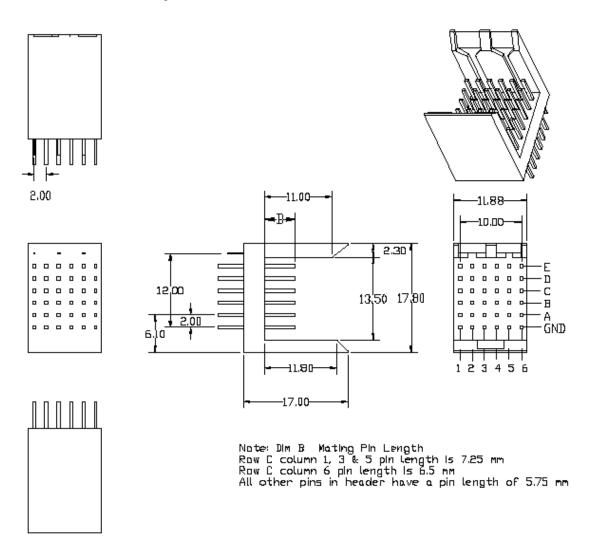

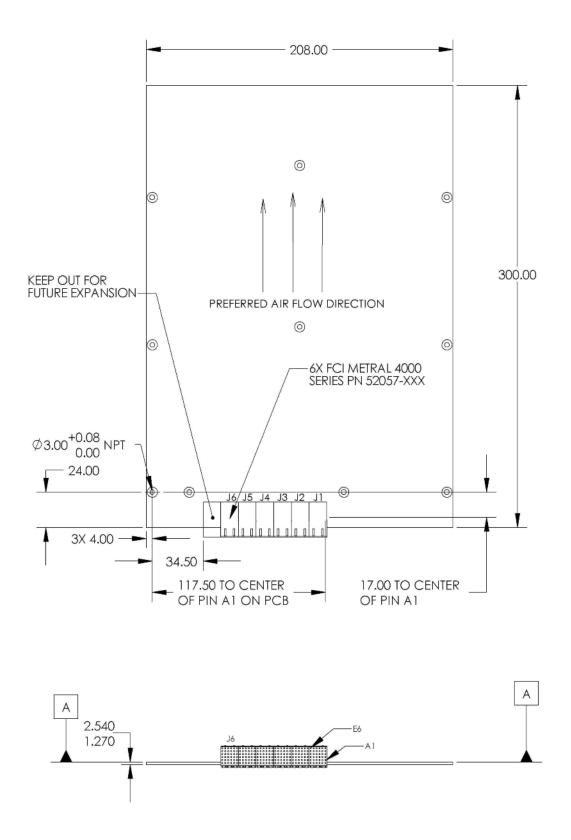

| D.4      | I/O Controller Module Connectors                   |     |

| D.4.     |                                                    |     |

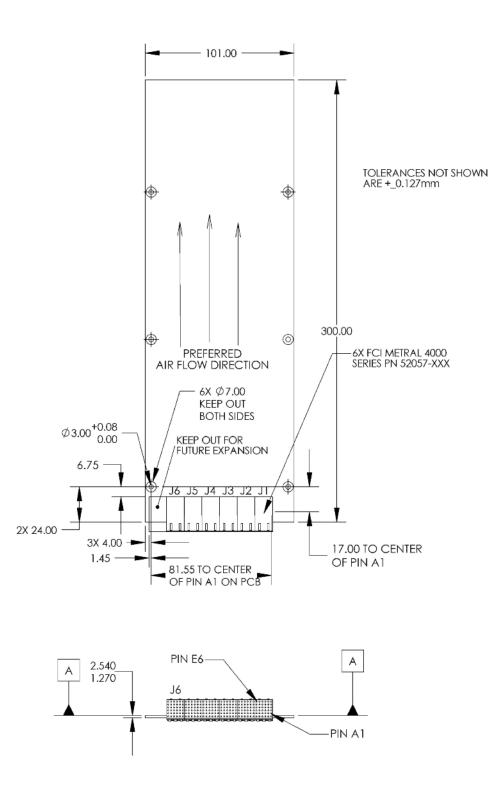

| D.5      | I/O Controller Module Connector Locations          |     |

| D.5.     | I                                                  |     |

| D.6      | Pinout Listing                                     |     |

| D.7      | Signal Descriptions                                |     |

| Appendix |                                                    |     |

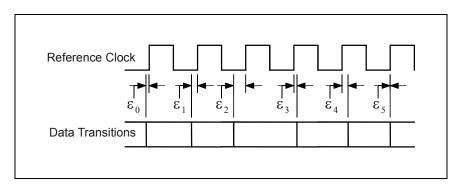

| E.1      | Clock to Data                                      |     |

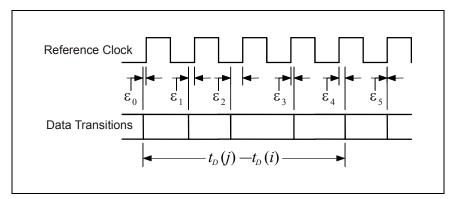

| E.2      | Data to Data (shown for historical reasons)        | 662 |

|          |                                                    |     |

## LIST OF FIGURES

| Figure 1 – Byte, word and Dword relationships                                                   | . 45 |

|-------------------------------------------------------------------------------------------------|------|

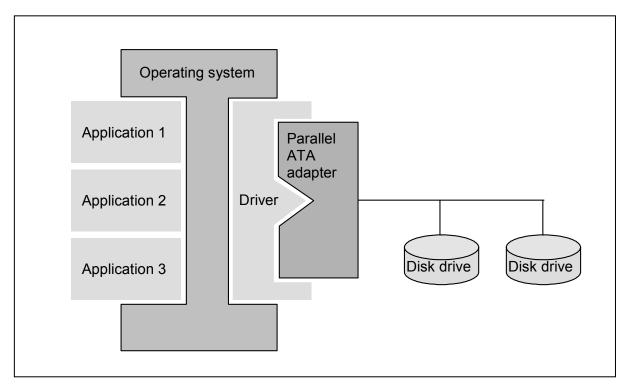

| Figure 2 – Parallel ATA device connectivity                                                     | . 47 |

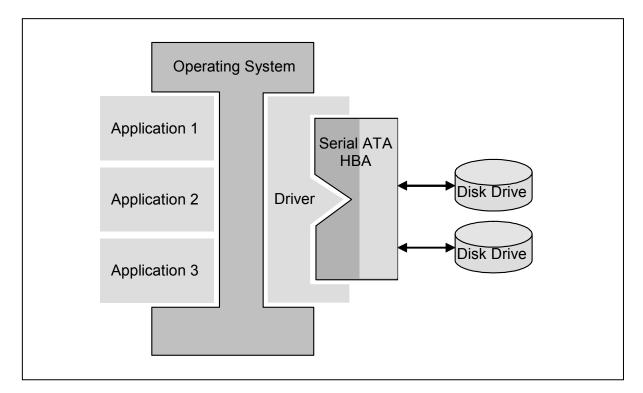

| Figure 3 – Serial ATA connectivity                                                              |      |

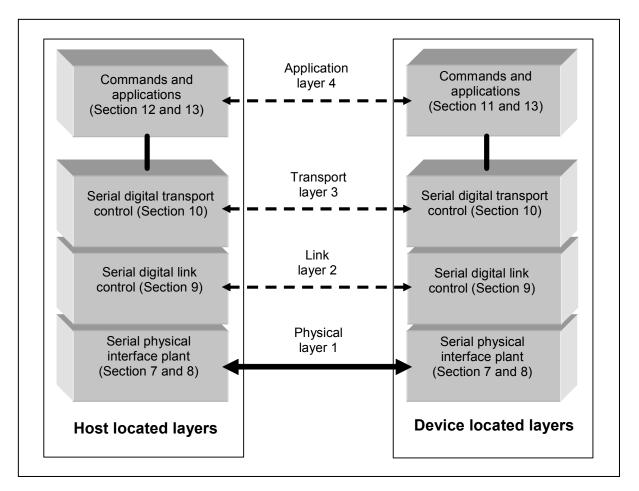

| Figure 4 – Communication layers                                                                 |      |

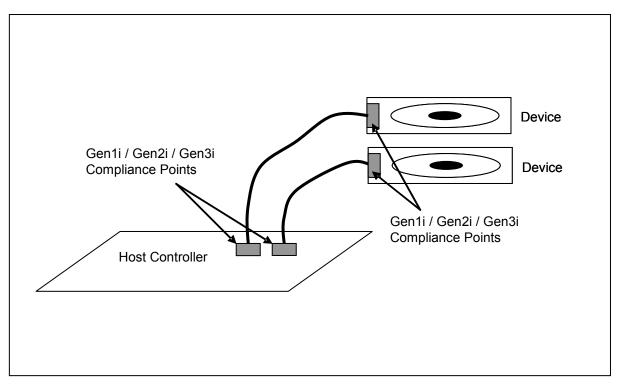

| Figure 5 – Internal 1 meter Cabled Host to Device Application                                   | . 52 |

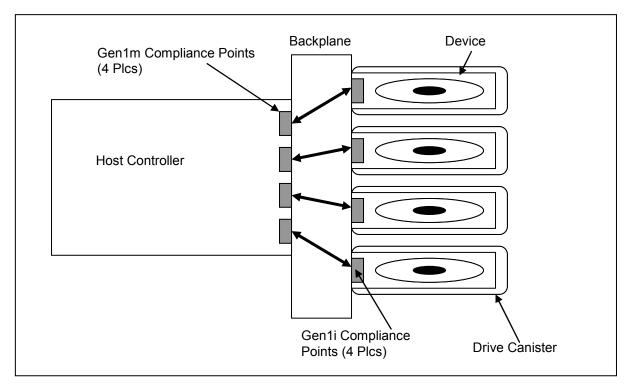

| Figure 6 – Short Backplane to Device Application                                                |      |

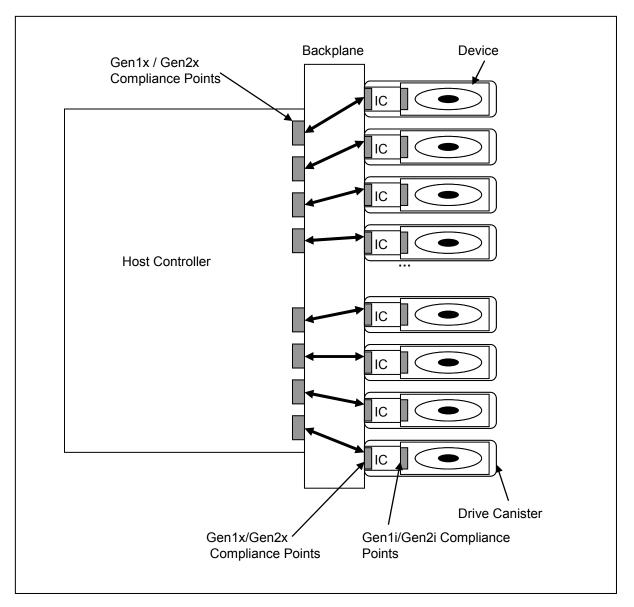

| Figure 7 – Long Backplane to Device Application                                                 |      |

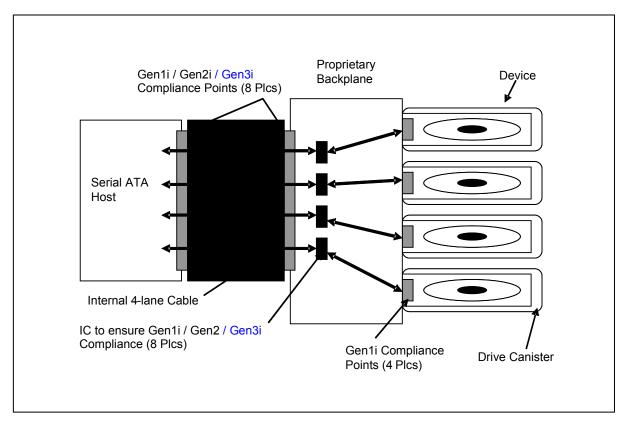

| Figure 8 – Internal 4-lane Cabled Disk Array                                                    |      |

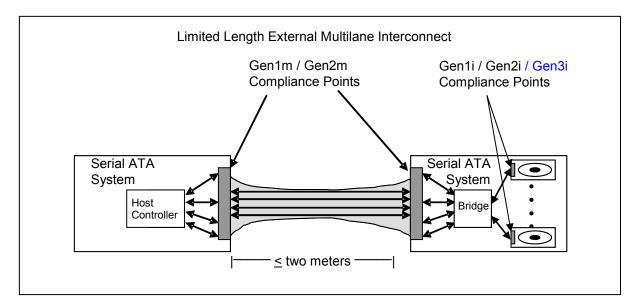

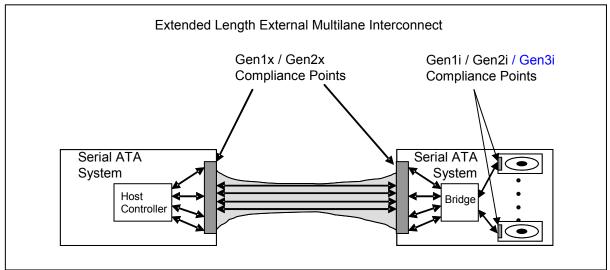

| Figure 9 – System-to-System Data Center Interconnects                                           |      |

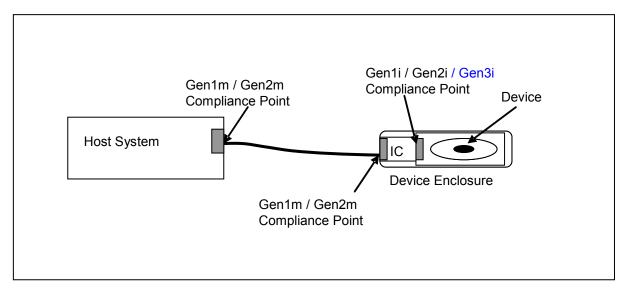

| Figure 10 – External Desktop Application                                                        |      |

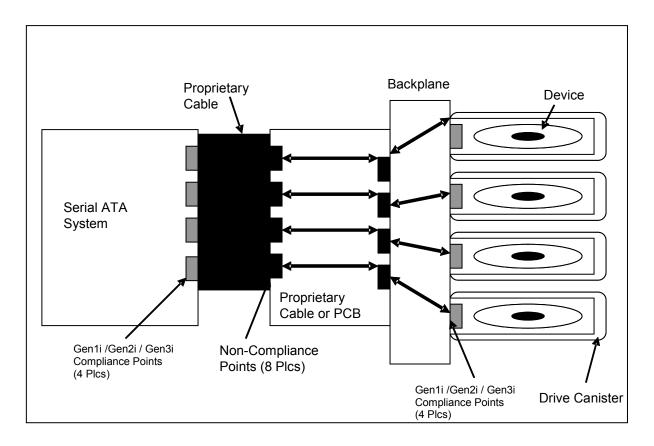

| Figure 11 – SATA Disk Arrays.                                                                   |      |

| Figure 12 - Embedded LIF-SATA Application                                                       |      |

| Figure 13 – Enclosure example using Port Multipliers with Serial ATA as the connection within   | the  |

| rack                                                                                            |      |

| Figure 14 – Enclosure example using Port Multipliers with a different connection within the rac |      |

| Figure 15 – Mobile docking station example using a Port Multiplier                              |      |

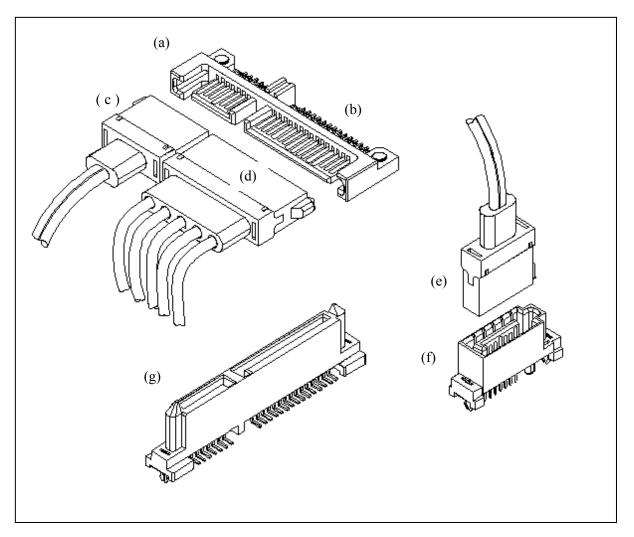

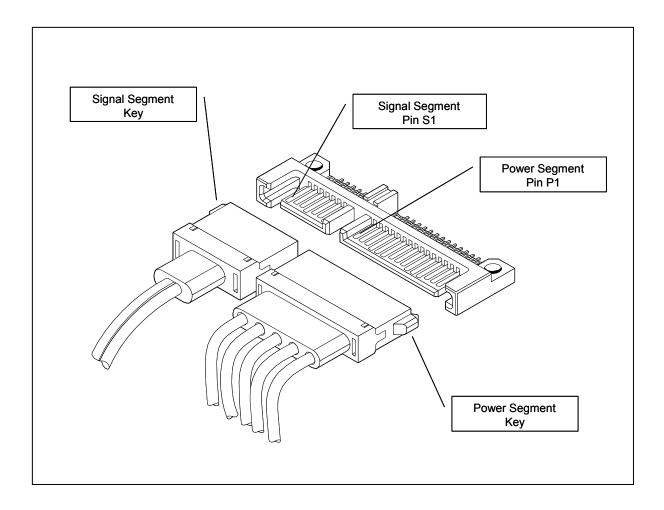

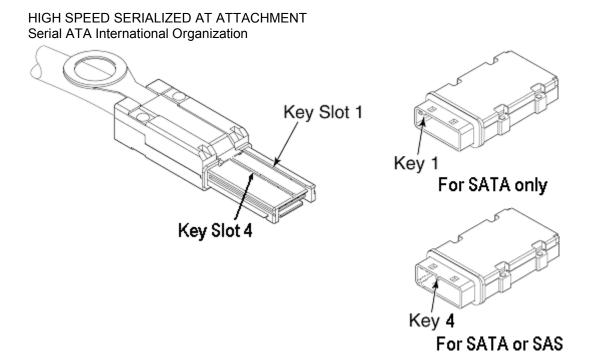

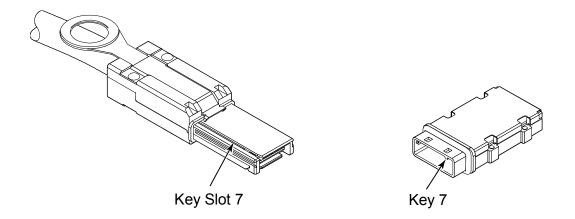

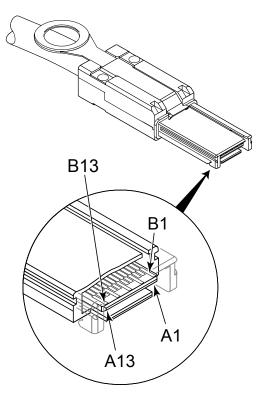

| Figure 16 – Serial ATA connector examples                                                       |      |

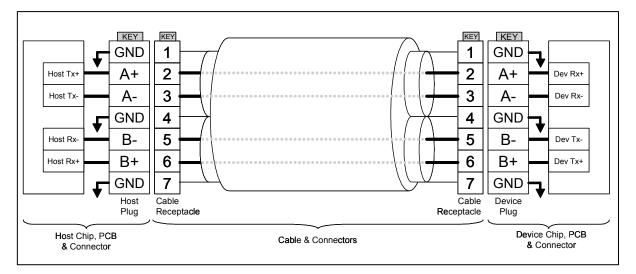

| Figure 17 – SATA Cable / Connector Connection Diagram                                           |      |

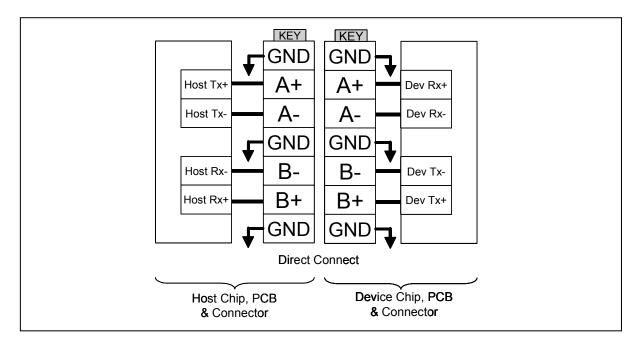

| Figure 18 – SATA Host / Device Connection Diagram                                               |      |

| Figure 19 – Optical Device Plug Connector Location on 5.25" form factor                         |      |

| Figure 20 – Non-Optical Alternate Device Plug Connector Location on 5.25" form factor           |      |

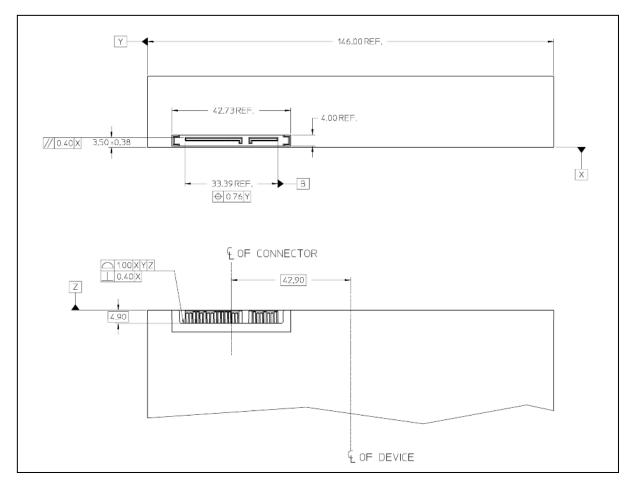

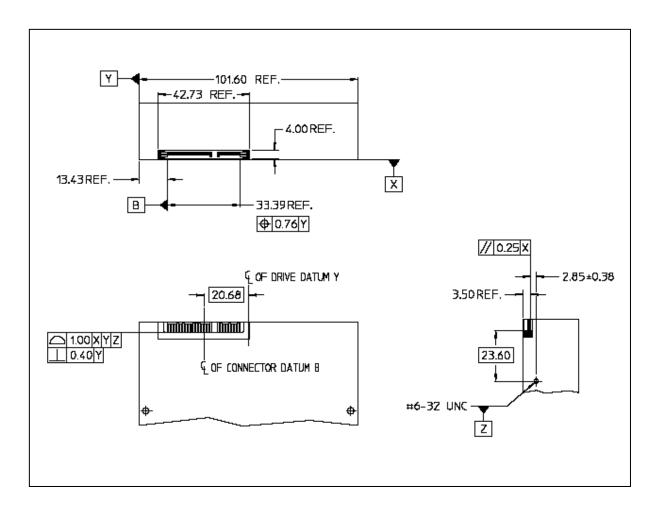

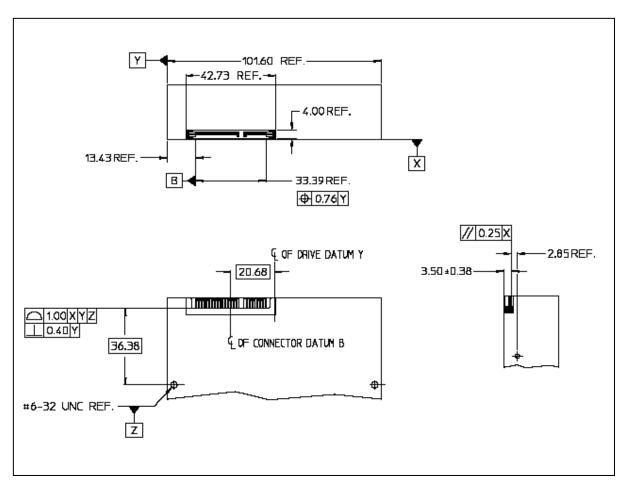

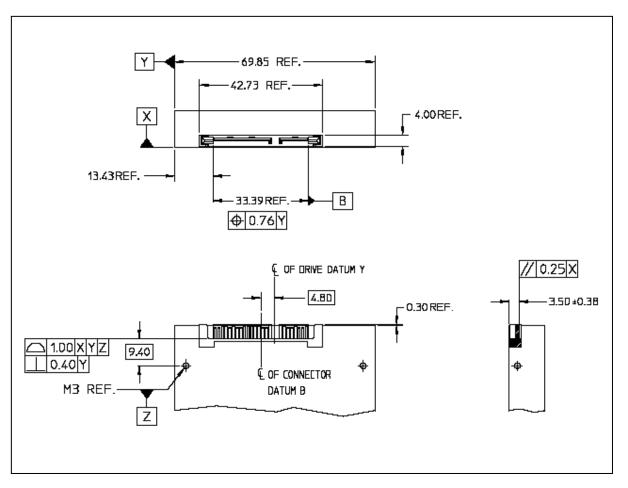

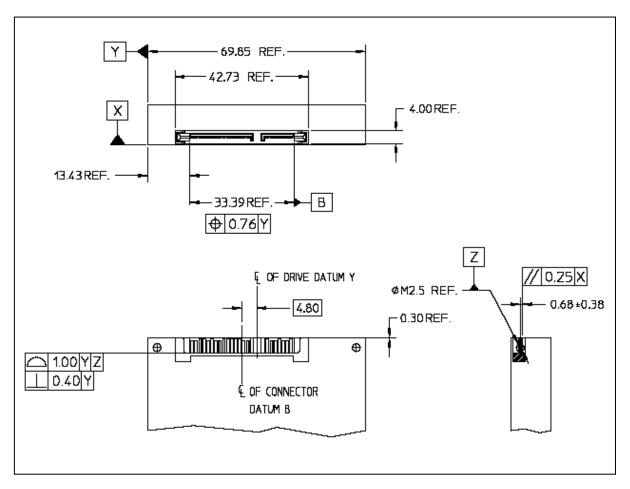

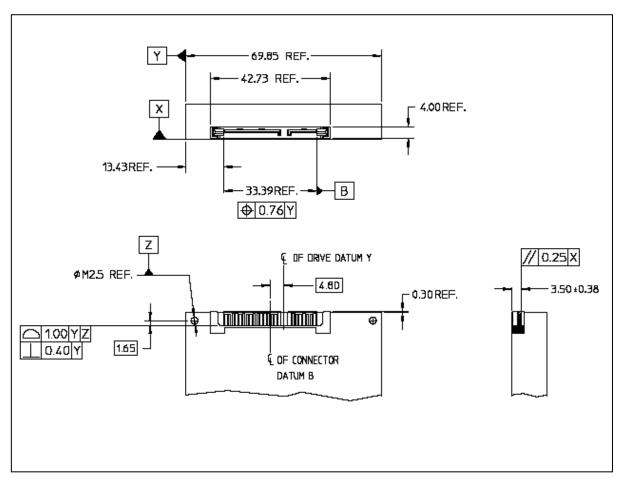

| Figure 21 – Device Plug Connector Location on 3.5" Side Mounted Device                          |      |

| Figure 22 – Device Plug Connector Location on 3.5" Side Mounted Device                          |      |

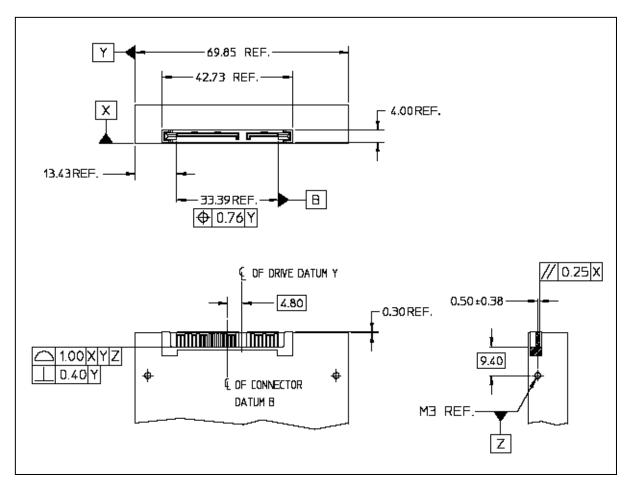

| Figure 23 – Device Plug Connector Location on 2.5" Side Mounted Device                          |      |

| Figure 23 – Device Flug Connector Location on 2.5" Side Mounted Device                          |      |

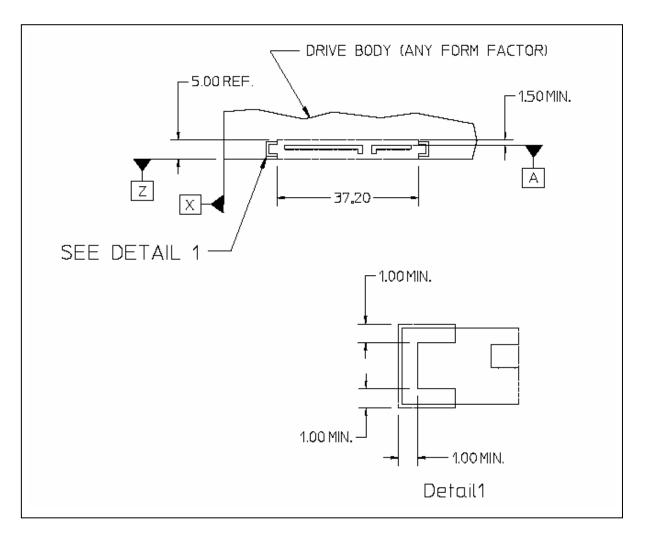

| Figure 25 – Device Plug Connector Location on 1.8" Side Mounted Device                          |      |

| Figure 26 – Device Plug Connector Location on 1.8" Bottom Mounted Device                        |      |

| Figure 26 – Device Flug Connector Keep Out Zones                                                |      |

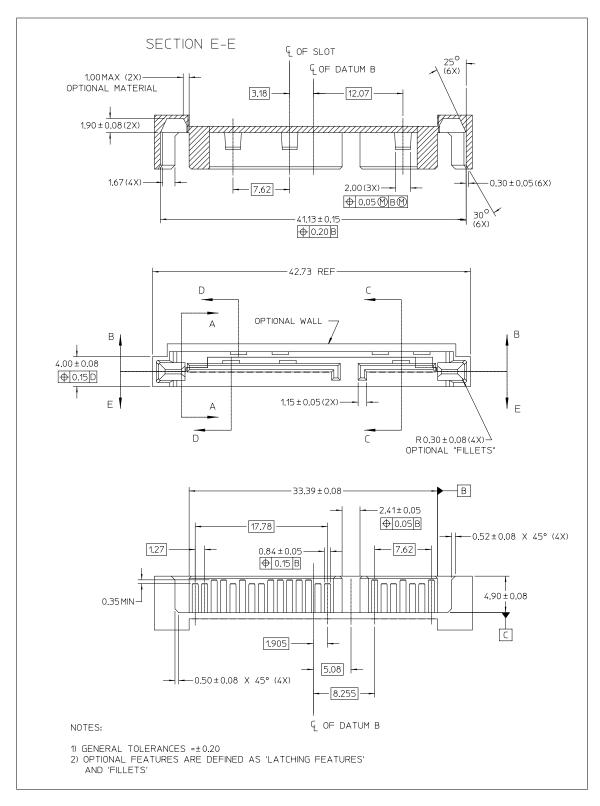

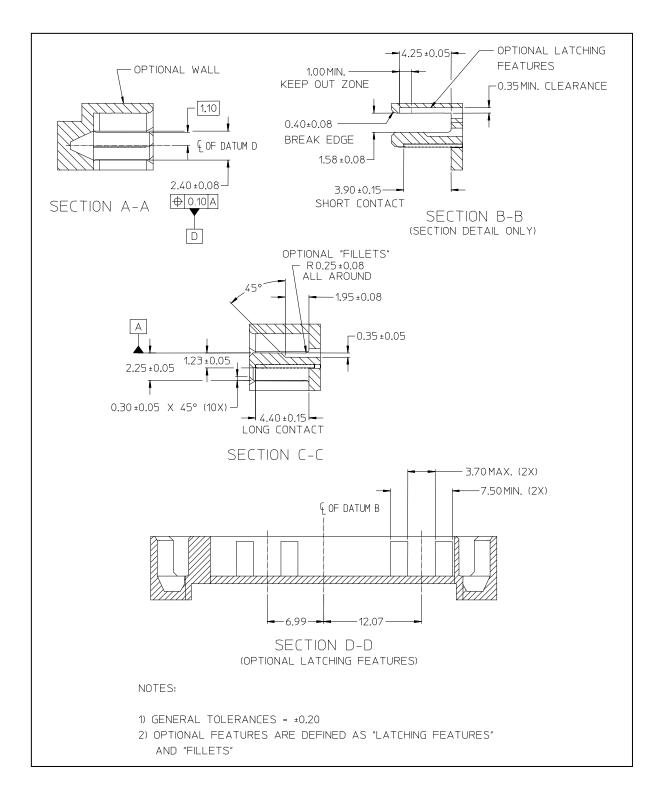

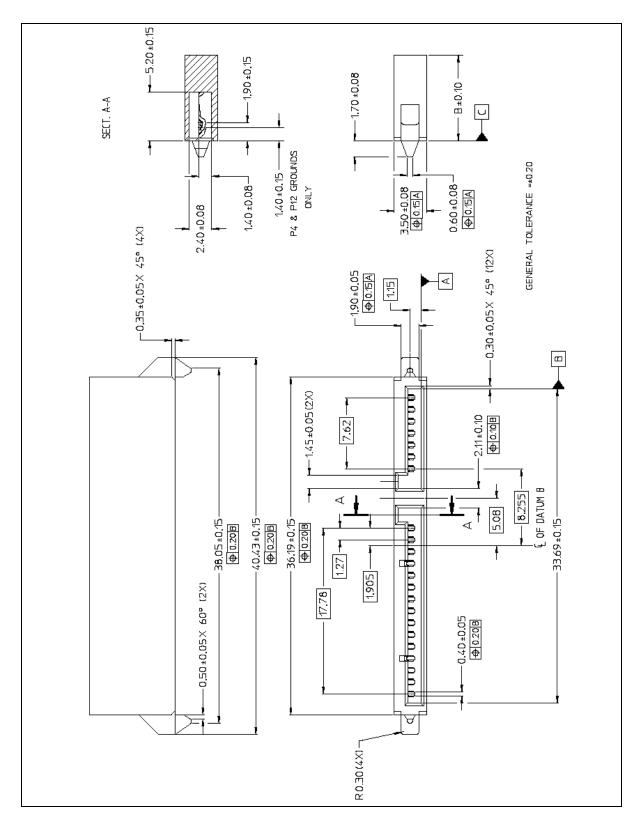

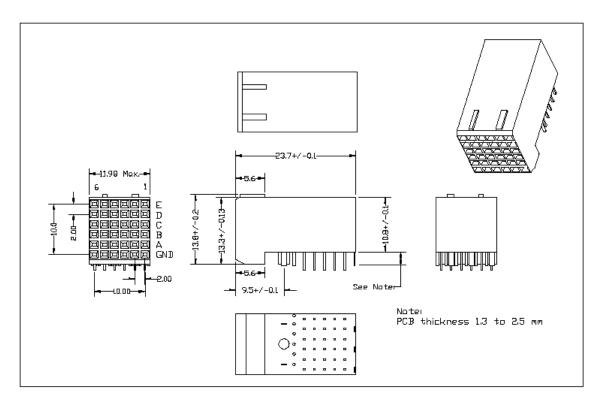

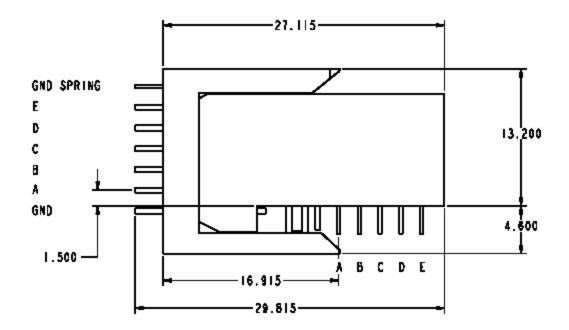

| Figure 28 – Device Plug Connector                                                               |      |

| Figure 29 – Device Plug Connector (additional views)                                            |      |

| Figure 30 – Connector Pin and Feature Locations                                                 |      |

|                                                                                                 |      |

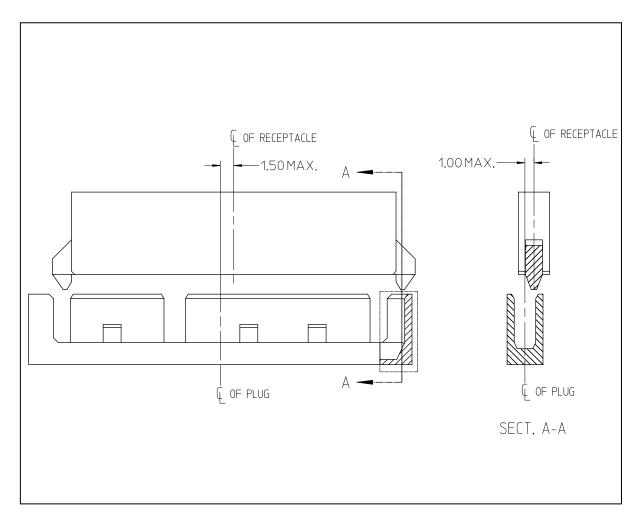

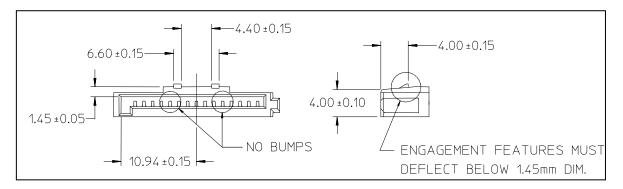

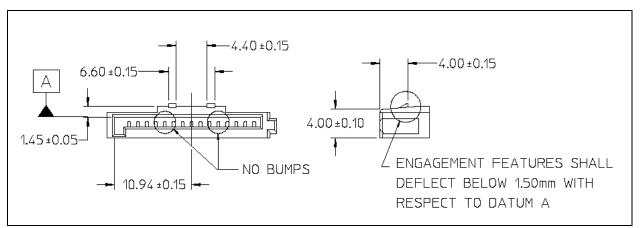

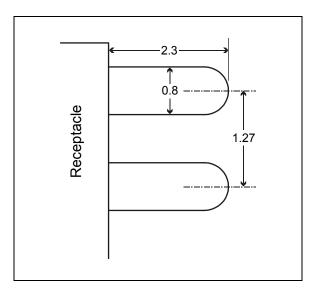

| Figure 31 – Cable receptacle connector interface dimensions                                     |      |

| Figure 32 – Latching signal cable receptacle (ClickConnect)                                     |      |

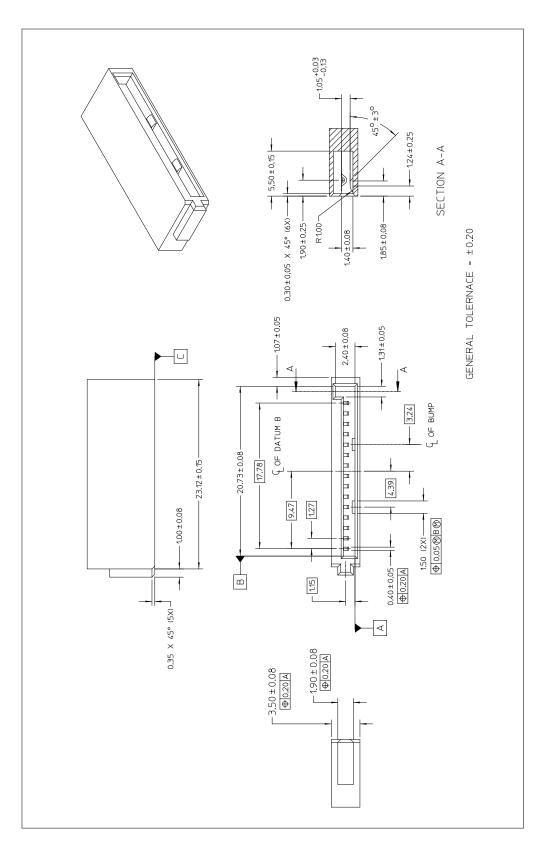

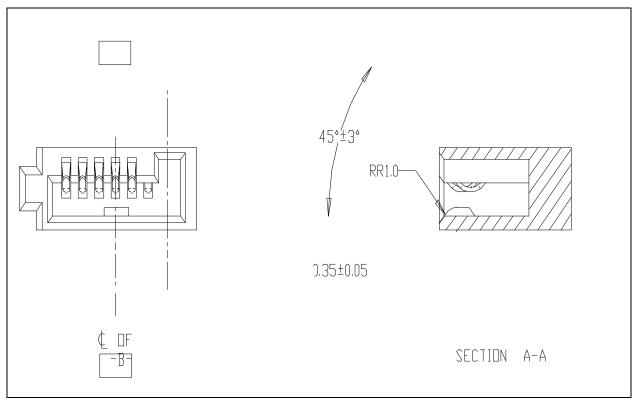

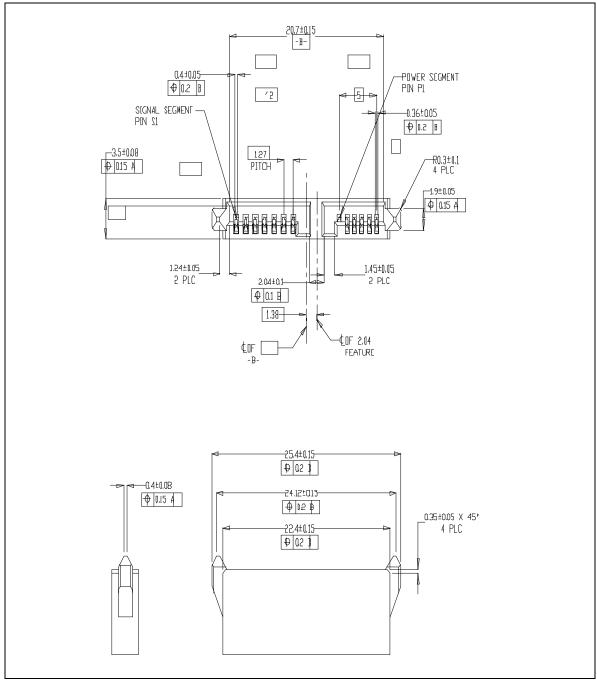

| Figure 33 – Host signal plug connector interface dimensions                                     |      |

| Figure 34 – Non-Latching Connector Stack Spacing and Orientation                                |      |

| Figure 35 – Latching Connector Stack Spacing and Orientation                                    |      |

| Figure 36 – Backplane connector interface dimensions.                                           |      |

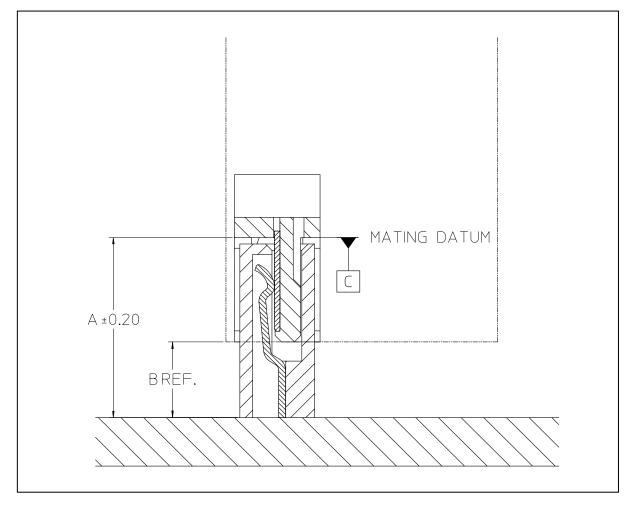

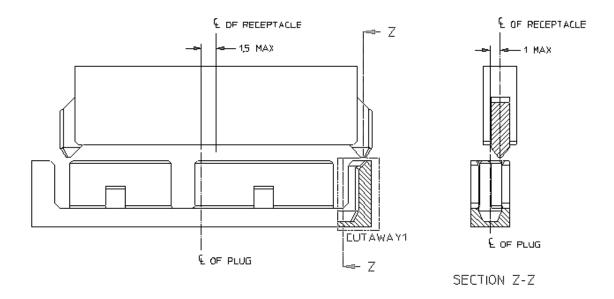

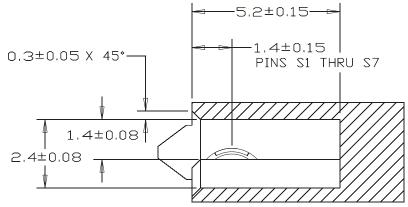

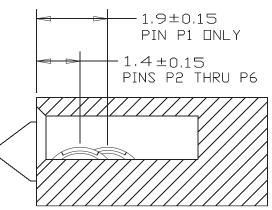

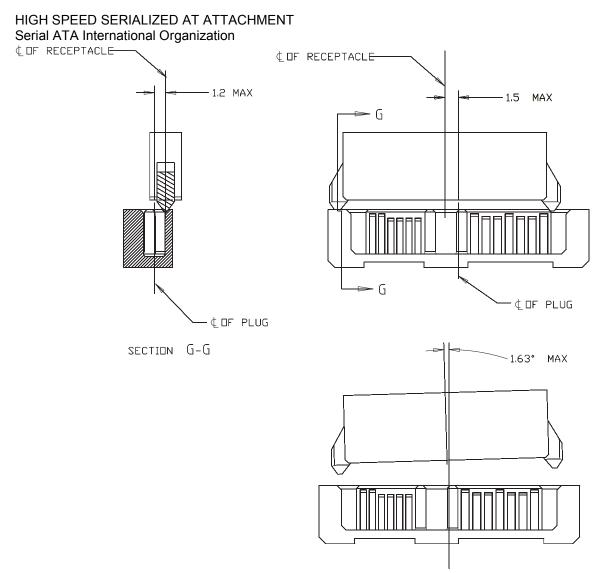

| Figure 37 – Connector pair blind-mate misalignment tolerance                                    |      |

| Figure 38 – Device-backplane mating configuration                                               |      |

| Figure 39 – Power receptacle connector interface dimensions                                     |      |

| Figure 40 – Latching power cable receptacle                                                     |      |

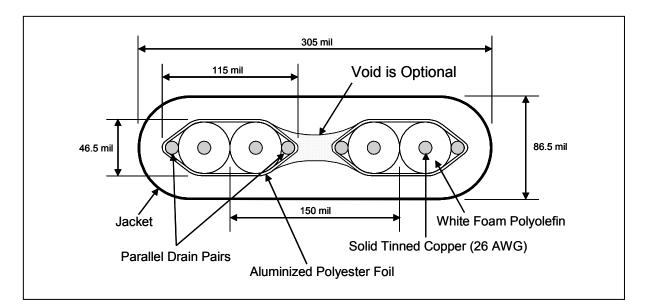

| Figure 41 – Detailed cross-section of an example internal single lane cable                     |      |

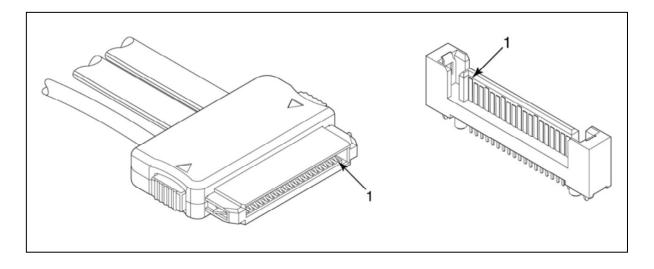

| Figure 42 – Isometric drawings of the internal 2 Lane cable and connector                       |      |

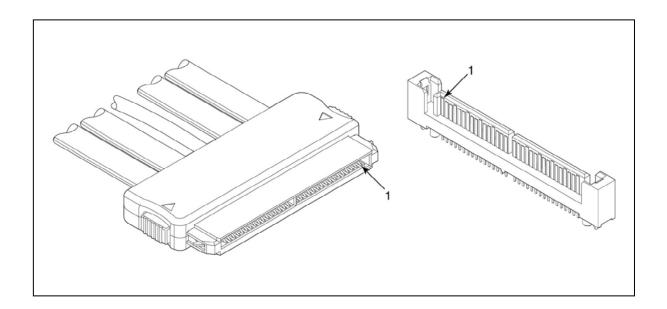

| Figure 43 – Isometric drawings of the internal 4 Lane cable and connector                       |      |

| Figure 44 – 4 Lane Pin Assignments.                                                             |      |

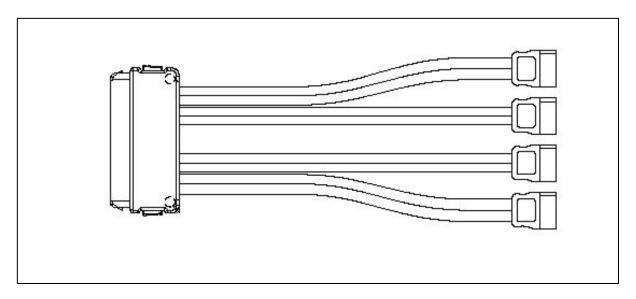

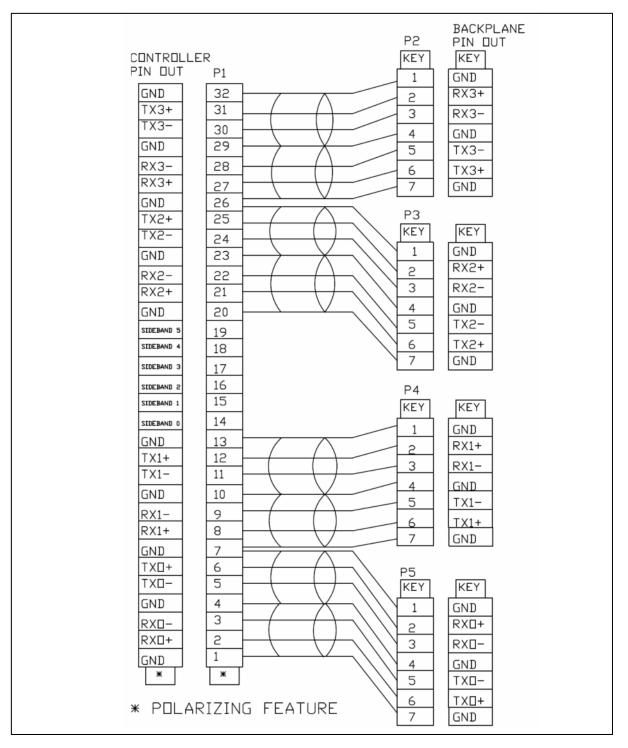

| Figure 45 – 4 Lane to 4 x 1 Lanes, Fanout Implementation                                        |      |

| Figure 46 – 4 Lane Fanout Pin Assignments                                                       |      |

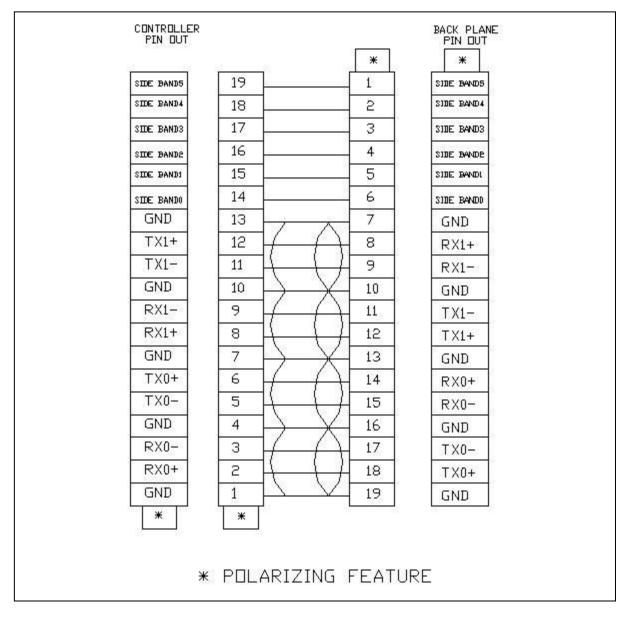

| Figure 47 – 2 Lane Fanout Pin Assignments                                                       | 104  |

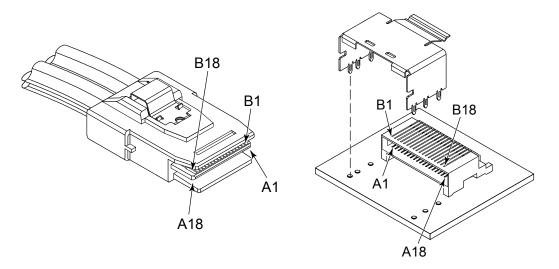

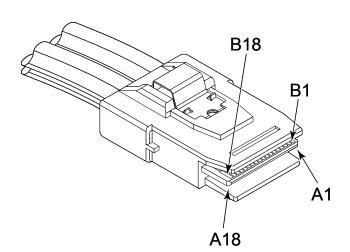

| Figure 48 Isometric Drawings for Mini SATA Internal Multilane                                   |      |

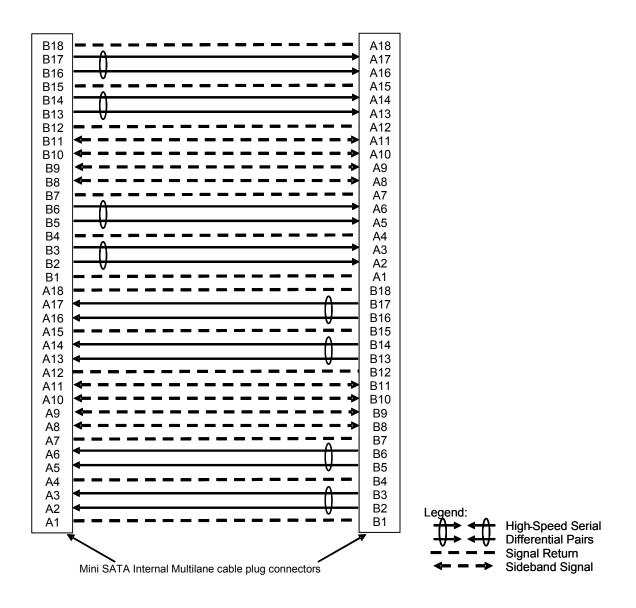

| Figure 49 Mini SATA Internal Multilane Connector Pin Assignments                                |      |

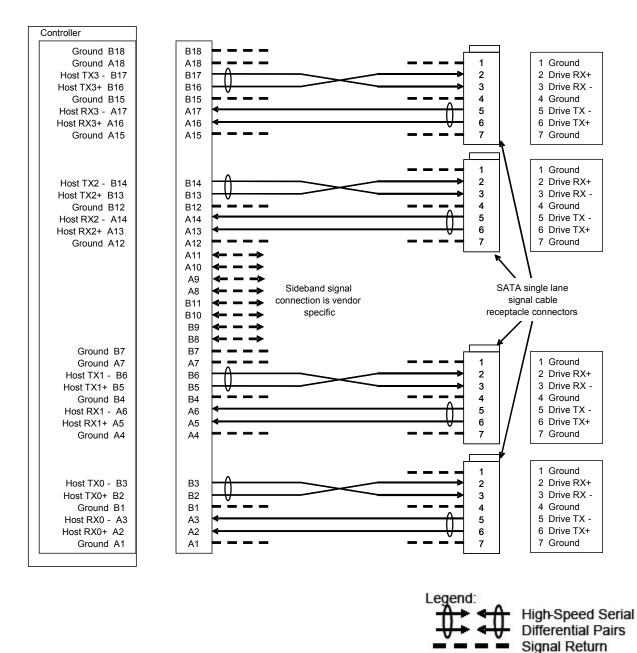

| Figure 50 Mini SATA Internal Multilane System, Symmetric Cable Implementation                   |      |

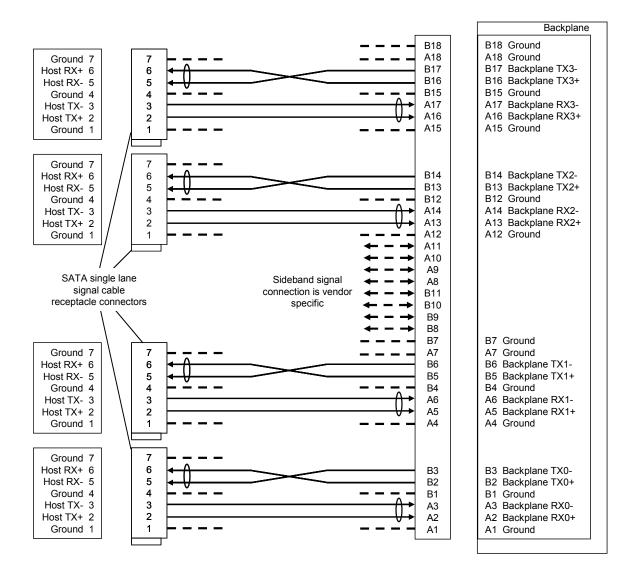

| Figure 51 Mini SATA Internal Multilane System, Controller based fanout cable implementa         |      |

|                                                                                                 | 109  |

| Figure 53       Device internal micro SATA connector location for 1.8" HDD.       112         Figure 50       Device internal micro SATA buckplane connector       113         Figure 56       Internal micro SATA buckplane connector       116         Figure 57       Internal micro SATA power receptable connector       117         Figure 50       5.5 mm/12.7 mm Silmiline Drive Connector Locations       122         Figure 61       7.0 mm Silmiline Drive Connector Location (Section A-A)       124         Figure 63       5.5 mm Silmiline Drive Connector Location (Section A-A)       124         Figure 63       5.7 0 mm Silmiline Drive Connector Location (Section A-A)       125         Figure 64       7.0 mm Silmiline device plug connector interface dimensions Section A-A       127         Figure 65       7.0 mm Silmiline device plug connector interface dimensions detail D       127         Figure 65       7.0 mm Silmiline device plug connector interface dimensions detail D       127         Figure 65       7.0 mm Silmiline device plug connector interface dimensions (Section A-A)       129         Figure 66       7.0 mm Silmiline device plug connector interface dimensions (Section A-A)       130         Figure 71       Silmiline Device plug connector interface dimensions (Section A-A)       130         Figure 73       Silmiline Device plug connector interface dimensions (Sect                                                                                                                                                                                                          | Figure 52 Mini SATA Internal Multilane System, Backplane based fanout cable implement   |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|

| Figure 54       Device internal micro SATA poly connector.       116         Figure 56       Internal micro SATA power receptable connector.       116         Figure 56       Internal micro SATA power receptable connector.       117         Figure 56       Internal micro SATA power receptable connector.       117         Figure 57       Internal micro SATA connector pair bilnd-mate misalignment capability.       118         Figure 61       7.0 mm Slimline Drive Connector Location (Section A-A).       124         Figure 62       9.5 mm Slimline Drive Connector Location (Section A-A).       124         Figure 63       12.7 mm Slimline Drive Connector Interface dimensions Section A-A.       125         Figure 64       7 0 mm Slimline device plug connector interface dimensions Section A-A.       127         Figure 65       7.0 mm Slimline device plug connector interface dimensions Section A-A.       127         Figure 65       7.0 mm Slimline device plug connector interface dimensions (Section A-A).       130         Figure 70       Slimline Device plug connector interface dimensions (Section A-A).       130         Figure 71       Slimline Device plug connector interface dimensions (Section A-A).       130         Figure 72       Slimline Device plug connector interface dimensions (Section A-A).       130         Figure 73       Slimline Device plug connector interface d                                                                                                                                                                                                          | Figure 53 Device internal micro SATA connector location for 1.8" HDD                    | . 112 |

| Figure 55         Device internal micro SATA plug connector.         116           Figure 56         Internal micro SATA backplane connector         116           Figure 57         Internal micro SATA connector pair blind-mate misalignment capability.         117           Figure 50         Internal micro SATA connector Locations.         122           Figure 60         9.5 mm/12.7 mm Slimline Drive Connector Location (Section A-A).         124           Figure 61         7.0 mm Slimline Drive Connector Location (Section A-A).         124           Figure 62         9.5 mm Slimline Drive Connector Location (Section A-A).         125           Figure 63         7.0 mm Slimline device plug connector interface dimensions Section B-B.         127           Figure 67         7.0 mm Slimline device plug connector interface dimensions optional hold down mounting         127           Figure 68         Slimline Device plug connector interface dimensions (Section A-A).         130           Figure 71         Slimline Device plug connector interface dimensions (Section A-A).         130           Figure 73         Slimline Device plug connector interface dimensions (Section A-A).         130           Figure 74         Slimline Device plug connector interface dimensions (Section A-A).         130           Figure 75         Slimline Device plug connector interface dimensions (Section A-A).         130                                                                                                                                                                                  |                                                                                         |       |

| Figure 57       Internal micro SATA power receptable connector       117         Figure 58       Internal micro SATA connector pair blind-mate misalignment capability       118         Figure 60       9.5 mm/12.7 mm Slimiline Drive Connector Locations       122         Figure 61       7.0 mm Slimiline Drive Connector Location (Section A-A)       124         Figure 62       9.5 mm Slimiline Drive Connector Location (Section A-A)       124         Figure 63       7.0 mm Slimiline device plug connector interface dimensions Section A-A       125         Figure 64       7.0 mm Slimiline device plug connector interface dimensions Section B-B       127         Figure 66       7.0 mm Slimiline device plug connector interface dimensions optional hold down mounting       127         Figure 69       Slimilne Device plug connector interface dimensions (Section A-A)       130         Figure 71       Slimilne Device plug connector interface dimensions (Section A-A)       130         Figure 72       Slimilne Device plug connector interface dimensions (Section A-A)       130         Figure 73       Slimiline Device plug connector interface dimensions (Section A-A)       130         Figure 74       Slimiline Device plug connector interface dimensions (Section A-A)       130         Figure 74       Slimiline Device plug connector interface dimensions (Section A-A)       130         Figure 74 <td></td> <td></td>                                                                                                                                                                                |                                                                                         |       |

| Figure 58       Internal micro SATA connector pair bilind-mate misalignment capability.       118         Figure 60       9.5 mm/12.7 mm Slimiline Drive Connector Locations.       123         Figure 61       7.0 mm Slimiline Drive Connector Location (Section A-A).       124         Figure 62       9.5 mm Slimiline Drive Connector Location (Section A-A).       124         Figure 63       12.7 mm Slimiline Drive Connector Location (Section A-A).       125         Figure 64       -7.0 mm Slimiline device plug connector interface dimensions Section A-A.       127         Figure 65       -7.0 mm Slimiline device plug connector interface dimensions Section A-A.       127         Figure 65       -7.0 mm Slimiline device plug connector interface dimensions Section A-A.       127         Figure 64       -7.0 mm Slimiline device plug connector interface dimensions (Section A-A).       130         Figure 70       Slimiline Device plug connector interface dimensions (Section A-A).       130         Figure 71       Slimiline Device plug connector interface dimensions (Section A-A).       130         Figure 72       Slimiline Device plug connector interface dimensions (Section A-A).       130         Figure 73       Slimiline Device plug connector interface dimensions (Section A-A).       130         Figure 74       Slimiline Device plug connector interface dimensions (Section A-A).       130                                                                                                                                                                                               | Figure 56 Internal micro SATA backplane connector                                       | . 116 |

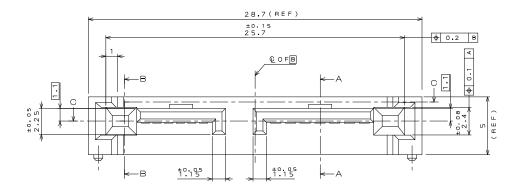

| Figure 59 - 7.0 mm Slimline Drive Connector Locations       122         Figure 61 - 7.0 mm Slimline Drive Connector Location (Section A-A)       124         Figure 62 - 9.5 mm Slimline Drive Connector Location (Section A-A)       124         Figure 63 - 12.7 mm Slimline Drive Connector Incation (Section A-A)       125         Figure 64 - 7 mm Slimline device plug connector interface dimensions Section A-A       127         Figure 65 - 7.0 mm Slimline device plug connector interface dimensions Section A-A       127         Figure 66 - 7.0 mm Slimline device plug connector interface dimensions Section A-A       127         Figure 66 - 7.0 mm Slimline device plug connector interface dimensions (Section A-A)       130         Figure 67 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 70 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 71 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 72 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 73 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 74 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 74 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 74 - Slimline Device plug connector interface dimensions (Section A-A)                                                                                                               |                                                                                         |       |

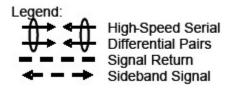

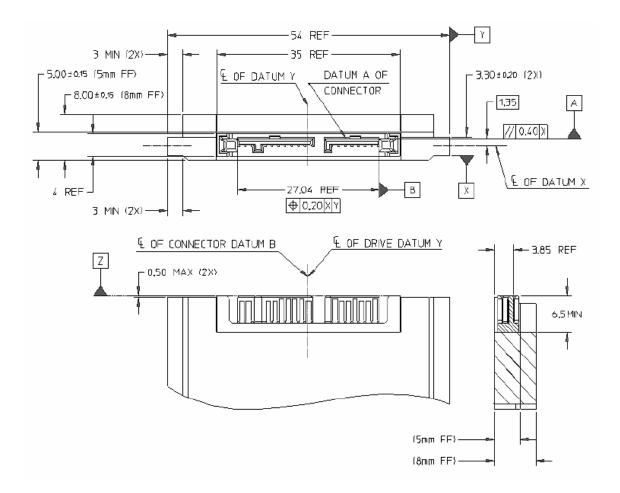

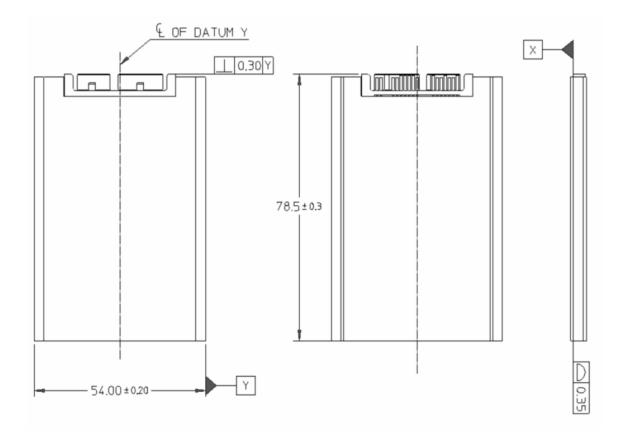

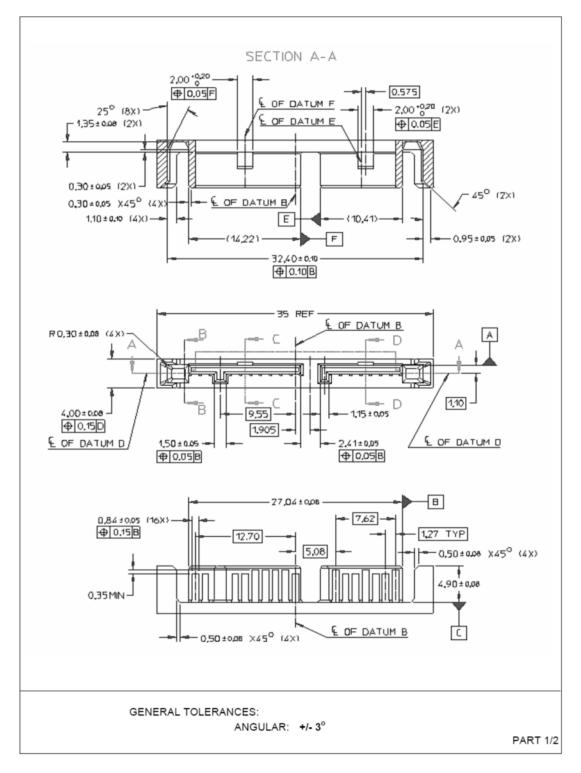

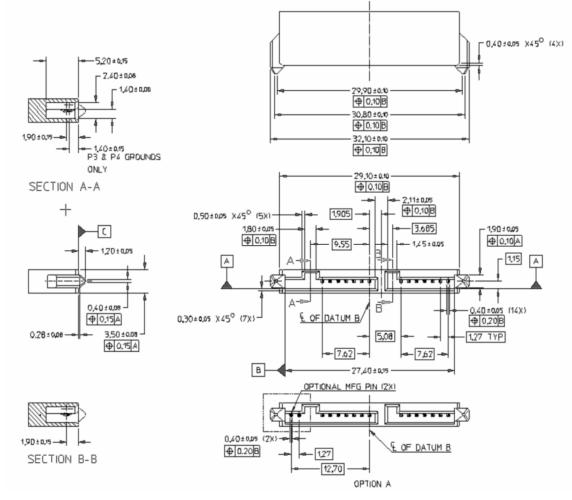

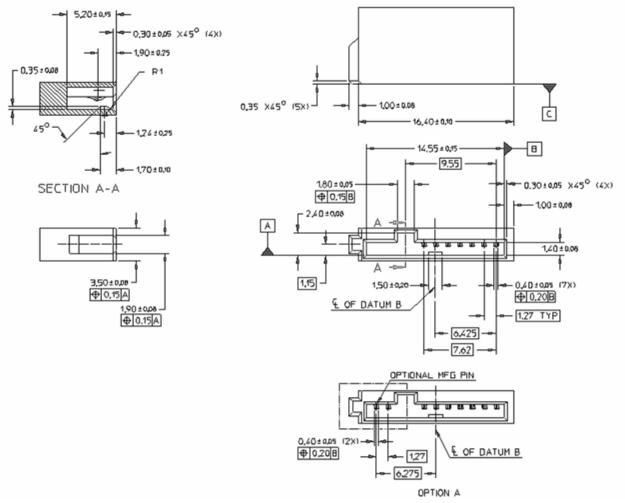

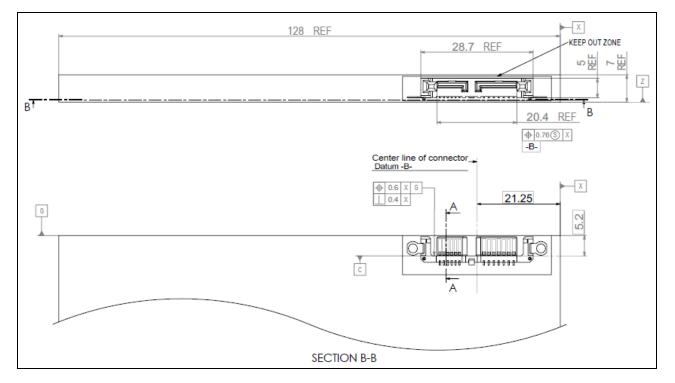

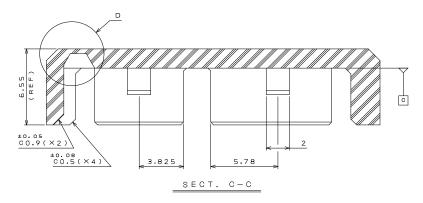

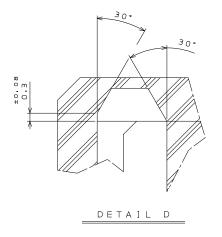

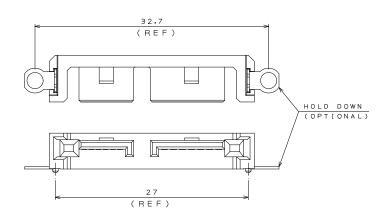

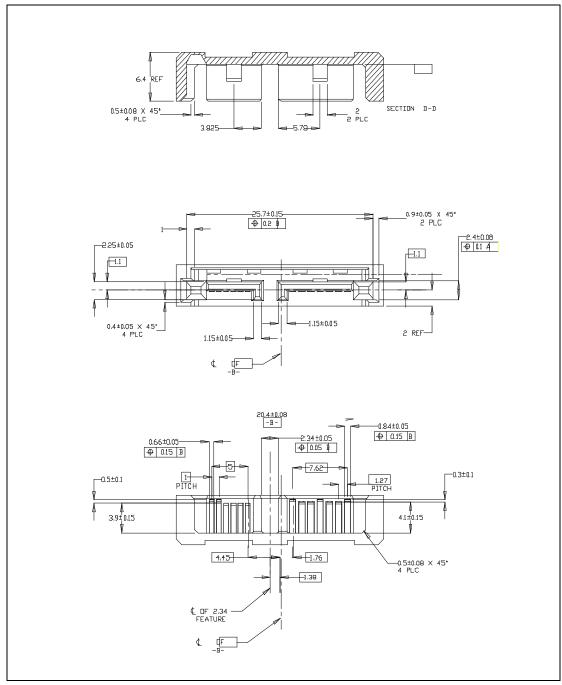

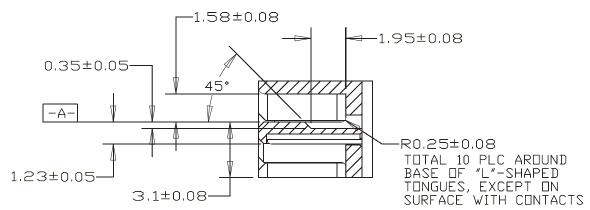

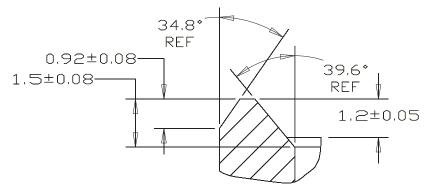

| Figure 60 - 9.5 mm/12.7 mm Slimline Drive Connector Locations.       123         Figure 61 - 7.0 mm Slimline Drive Connector Location (Section A-A)       124         Figure 62 - 9.5 mm Slimline Drive Connector Location (Section A-A)       125         Figure 63 - 7.0 mm Slimline device plug connector interface dimensions       126         Figure 64 - 7.0 mm Slimline device plug connector interface dimensions Section A-A       127         Figure 65 - 7.0 mm Slimline device plug connector interface dimensions Section A-A       127         Figure 66 - 7.0 mm Slimline device plug connector interface dimensions detail D       127         Figure 68 - 7.0 mm Slimline device plug connector interface dimensions detail D       127         Figure 69 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 70 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 71 - Slimline Device plug connector interface dimensions (Section C-C)       130         Figure 72 - Slimline Device plug connector interface dimensions (Section C-C)       130         Figure 75 - Slimline Device Plug connector interface dimensions (Section A-A)       130         Figure 76 - Slimline Device Plug connector interface dimensions (Section A-A)       130         Figure 77 - Slimline Device Plug connector interface dimensions (Section A-A)       133         Figure 78 - Slimline Device Plug connector interface dimensions (Section A-A) <td>Figure 58 Internal micro SATA connector pair blind-mate misalignment capability</td> <td>. 118</td> | Figure 58 Internal micro SATA connector pair blind-mate misalignment capability         | . 118 |

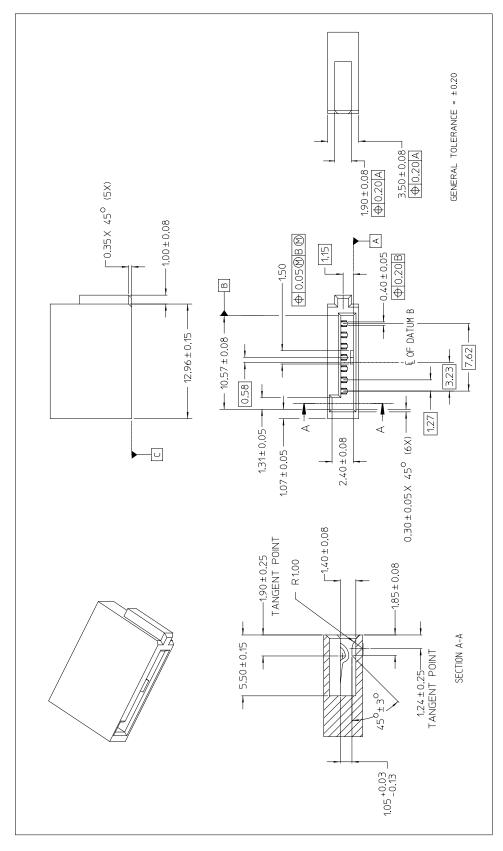

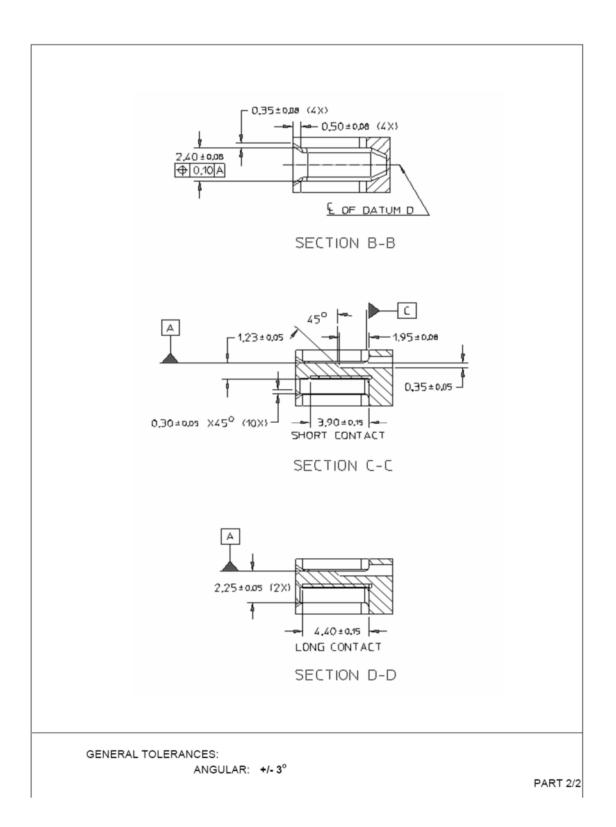

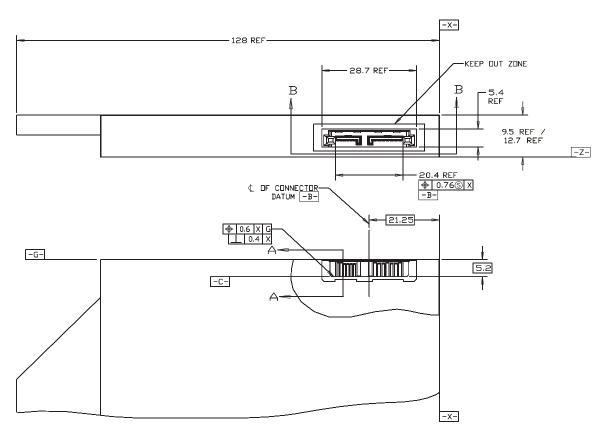

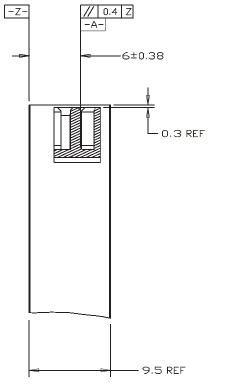

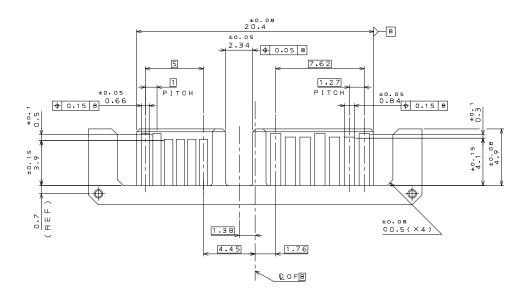

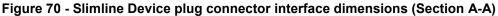

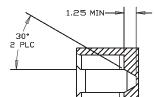

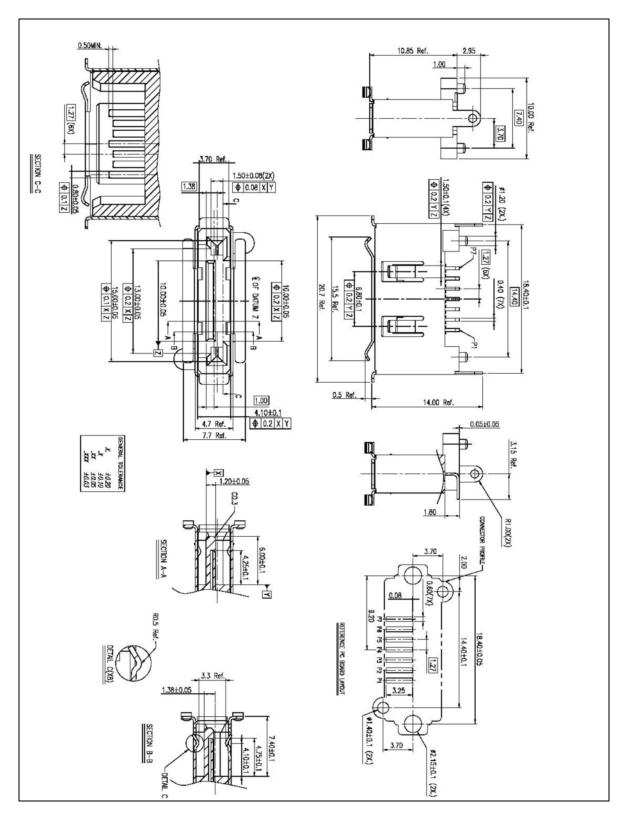

| Figure 61 - 7.0 mm Slimline Drive Connector Location (Section A-A)       124         Figure 62 - 9.5 mm Slimline Drive Connector Location (Section A-A)       124         Figure 63 - 12.7 mm Slimline device plug connector interface dimensions Section A-A)       125         Figure 66 - 7.0 mm Slimline device plug connector interface dimensions Section A-A       127         Figure 67 - 7.0 mm Slimline device plug connector interface dimensions Section A-A       127         Figure 68 - 7.0 mm Slimline device plug connector interface dimensions optional hold down mounting       127         Figure 69 - 7.0 stimline Device plug connector interface dimensions optional hold down mounting       129         Figure 70 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 71 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 73 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 74 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 74 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 74 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 74 - Slimline Device Plug connector interface dimensions (Section A-A)       130         Figure 74 - Slimline Device Plug connector interface dimensions (Section A-A)       130         Figure 74 - Slim                                                                                                      |                                                                                         |       |

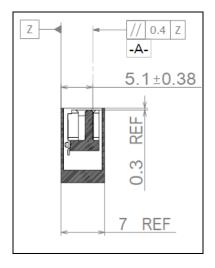

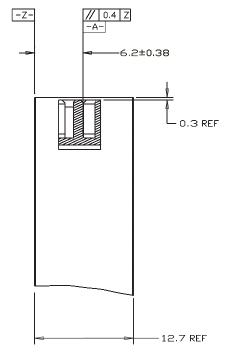

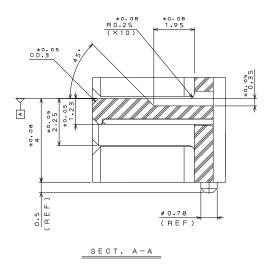

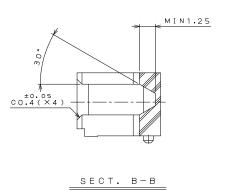

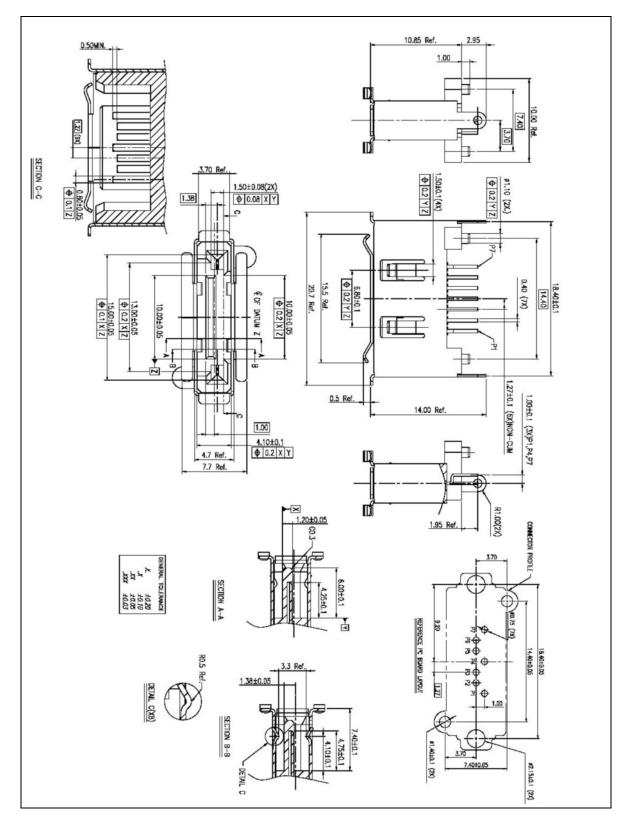

| Figure 62 - 9.5 mm Slimline Drive Connector Location (Section A-A)       124         Figure 63 - 12.7 mm Slimline device plug connector interface dimensions       125         Figure 64 - 7 mm Slimline device plug connector interface dimensions Section B-A       127         Figure 67 - 7.0 mm Slimline device plug connector interface dimensions Section B-B       127         Figure 68 - 7.0 mm Slimline device plug connector interface dimensions Section B-B       127         Figure 69 - 7.0 mm Slimline device plug connector interface dimensions optional hold down mounting       127         Figure 70 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 71 - Slimline Device plug connector interface dimensions (Section A-A)       130         Figure 72 - Slimline Device plug connector interface dimensions (Section C-C)       130         Figure 73 - Slimline Device plug connector interface dimensions (Section C-C)       130         Figure 74 - Slimline Device plug connector interface dimensions       132         Figure 75 - Slimline Device plug connector optional Hold Down Mounting       133         Figure 76 - Slimline Device plug connector interface dimensions       132         Figure 77 - Slimline Power receptacle connector Option with Latch       133         Figure 78 - Slimline Power receptacle connector interface dimensions       133         Figure 80 - Slimline Host receptacle connector interface dimensions Section C-C                                                                                                                | Figure 60 - 9.5 mm/12.7 mm Slimline Drive Connector Locations                           | . 123 |